|

Why Gladiator CLD?

|

Dear Customers,

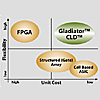

글로벌 로직 디바이스 업체인 Leopard Logic사는 업계 최초로 ASIC과 FPGA 기술의 장점을 결합한 로직 디바이스 Gladiator CLD 제품군을 출시했다. Gladiator CLD는 FPGA에서 처럼 설계를 즉시 변경할 수 있으면서, 설계 내에서 변경되지 않는 부분에 대해서는 효율적인 ASIC과 같은 구조로 고정시킬 수 있는, 사용자가 재구성 가능한 디바이스 제품이다.

두 기술의 결합으로, 여타의 솔루션보다 훨씬 저렴한 가격으로 초고속 설계, 저전력 소모 그리고 빠른 설계 변경을 할 수 있는 새로운 표준을 제시하게 됐다!

The Next Generation Configurable Logic Device

Gladiator CLD 제품군은 최대 2천5백만 시스템 게이트 및 10메가비트의 온-칩 메모리를 가지고 있는 제품까지 총 5가지의 디바이스로 구성돼 있으며, 500MHz 클럭 스피드로 동작한다. Gladiator 제품은 이미 정의된 기능에 의해 제한되지 않으므로, 고속의 처리가 필요한 많은 부분을 프로그래밍 가능한 마스크 영역(MP)에 설계 가능하기 때문에, 고객들의 특정 적용분야에 있어서 핵심 부품이 될 수 있을 것이다. Gladiator CLD 제품군은 최대 2천5백만 시스템 게이트 및 10메가비트의 온-칩 메모리를 가지고 있는 제품까지 총 5가지의 디바이스로 구성돼 있으며, 500MHz 클럭 스피드로 동작한다. Gladiator 제품은 이미 정의된 기능에 의해 제한되지 않으므로, 고속의 처리가 필요한 많은 부분을 프로그래밍 가능한 마스크 영역(MP)에 설계 가능하기 때문에, 고객들의 특정 적용분야에 있어서 핵심 부품이 될 수 있을 것이다.

또한 필드 프로그래밍 블록을 사용하여 추가적으로 설계 변경을 할 수 있어서, 새로운 비트 스트림을 디바이스에 간단히 다운로딩 함으로써 횟수에 관계없이 설계 변경이 가능하다. MP와 FP 블록은 동일한 구조를 갖고 있어서, Leopard Logic사의 설계툴을 사용하여 언제든지 재배치할 수 있다.

Read the full story...

|

|

Today's Design Dilemma |

|

|

Changing Standards: 통신규약, 데이타 포맷, 버스 인터페이스와 같은 기술적인 표준들은 끊임없이 변화한다. 빠르게 진화하는 기술규격과 급변하는 시장의 요구로 인해 언제나 변함없는 상호간 정보처리 운용을 요구하게 되었다. 시스템 설계자들은 한정된 예산 안에서, 이러한 변화에 대처함과 동시에 기존 제품개발에 소요되는 시간을 단축해야 한다. Changing Standards: 통신규약, 데이타 포맷, 버스 인터페이스와 같은 기술적인 표준들은 끊임없이 변화한다. 빠르게 진화하는 기술규격과 급변하는 시장의 요구로 인해 언제나 변함없는 상호간 정보처리 운용을 요구하게 되었다. 시스템 설계자들은 한정된 예산 안에서, 이러한 변화에 대처함과 동시에 기존 제품개발에 소요되는 시간을 단축해야 한다.

Increasing Costs: ASIC에서의 마스크 비용과 설계 기간은 빠르게 증가하고 있다. 새로운 솔루션들은 이제 한정된 시간과 예산에 맞춰 고객이 주문한 로직 디바이스를 생산해야 하는 과제를 안게 됐다. 이러한 딜레마는 오늘날 FPGA 시장의 견인차 역할을 하게 되었으며, 현재 "Structured ASIC"이라고 불리는, 게이트 어레이 스타일의 디바이스들이 부활하게 되는 계기를 마련했다. 과도한 비용과 긴 설계기간 등을 이유로, 점차 셀 기반의 ASIC 설계방식은 외면당하고 있다. 이제 고객들은 보다 저렴한 비용이 드는 옵션을 선택하거나, 주문형 로직 디바이스를 주문방식이 아닌(off-the-shelf) ASSP로 바꾸고 있다.

Elusive Time to Volume: 오늘날 급변하는 시장은 경쟁력을 갖추기 위해 신속한 제품 개발을 요구한다. 최근의 통계들에 따르면, 전체 ASIC제품 중 약 50%는 초기생산부터 단종시까지의 수량이 100,000개를 초과하지 않으며, 약 1백2십만 게이트(800k개 로직과 400k 메모리) 정도에서 중간규모의 설계복잡도를 가진다. ASIC 제품들은 설계기간이 지나치게 길기 때문에, 정작 디바이스가 출시될 무렵에는 설계기반이 되는 기술규격들은 구식이 되어버리고 만다. 그리하여 사장되는 디바이스도 많았다. 반면, FPGA 제품들은 빠른 타임-투-마켓이라는 장점은 있으나, 하이 볼륨급의 설계에는 적합하지 못하다는 한계를 안고 있다. 결과적으로, 최적의 로직 디자인을 수행할 수 있는 실질적인 대안에 대한 수요는 여전히 늘고 있다. Elusive Time to Volume: 오늘날 급변하는 시장은 경쟁력을 갖추기 위해 신속한 제품 개발을 요구한다. 최근의 통계들에 따르면, 전체 ASIC제품 중 약 50%는 초기생산부터 단종시까지의 수량이 100,000개를 초과하지 않으며, 약 1백2십만 게이트(800k개 로직과 400k 메모리) 정도에서 중간규모의 설계복잡도를 가진다. ASIC 제품들은 설계기간이 지나치게 길기 때문에, 정작 디바이스가 출시될 무렵에는 설계기반이 되는 기술규격들은 구식이 되어버리고 만다. 그리하여 사장되는 디바이스도 많았다. 반면, FPGA 제품들은 빠른 타임-투-마켓이라는 장점은 있으나, 하이 볼륨급의 설계에는 적합하지 못하다는 한계를 안고 있다. 결과적으로, 최적의 로직 디자인을 수행할 수 있는 실질적인 대안에 대한 수요는 여전히 늘고 있다.

Learn More... »

|

|

|

Reasons to use Gladiator CLD |

|

|

Unmatched Capability: Gladiator CLD는 ASIC과 FPGA 기술을 단일 디바이스로 구현한 업계 최초의 솔루션이다. FPGA 블록이 통합돼 있어서 디버그 시에도 디바이스를 업데이트할 수 있을 뿐 아니라 필드에서 새로운 비트스트림을 간단히 다운로딩함으로써 설계 변경할 수 있다.

High Performance: Gladiator CLD는 최악의 조건에서도 내부 클럭 네트워크가 최고 500MHz의 클럭 스피드로 작동할 수 있게 설계돼 있으며, 동일한 설계를 FPGA에서 구동하는 것 보다 전력소모가 1/4에 불과하다. 또한 Gladiator CLD는 FPGA의 Power-on glitch 오류도 제거했다.

Fast Time to Market: 설계자가 디자인을 합성하고 , 컨피규레이션 데이터를 생성한 후, 샘플이 납품되기까지의 과정이 4주 이내에 가능하다. 아울러 저렴한 NRE 비용과 효율적인 설계수행 등 Gladiator CLD는 1k~100k개 사이의 수량에서 가장 저렴한 솔루션이다.

See it for yourself - schedule your evaluation today! »

|

| Quick Links... |

|

|

![]()