| Example of simulation |                                                            |  |

|-----------------------|------------------------------------------------------------|--|

|                       | latch                                                      |  |

|                       | © GDM —                                                    |  |

|                       |                                                            |  |

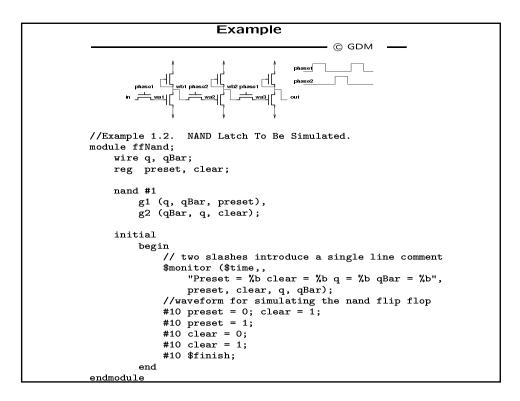

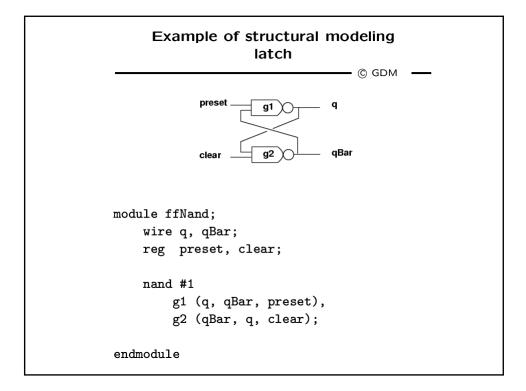

| //Example 1.          | 2. NAND Latch To Be Simulated.                             |  |

| module ffNar          | ıd;                                                        |  |

| wire q,               | qBar;                                                      |  |

| reg pre               | eset, clear;                                               |  |

| nand #1               |                                                            |  |

| g1 (                  | q, qBar, preset),                                          |  |

| g2 (                  | (qBar, q, clear);                                          |  |

| initial               |                                                            |  |

| begi                  | n                                                          |  |

| Ū.                    | <pre>// two slashes introduce a single line comment</pre>  |  |

|                       | <pre>\$monitor (\$time,,</pre>                             |  |

|                       | "Preset = $\%$ b clear = $\%$ b q = $\%$ b qBar = $\%$ b", |  |

|                       | preset, clear, q, qBar);                                   |  |

|                       | //waveform for simulating the nand flip flop               |  |

|                       | #10 preset = 0; clear = 1;                                 |  |

|                       | #10 preset = 1;                                            |  |

|                       | #10 clear = 0;                                             |  |

|                       | #10 clear = 1;                                             |  |

|                       | #10 \$finish;                                              |  |

| end                   |                                                            |  |

| endmodule             |                                                            |  |

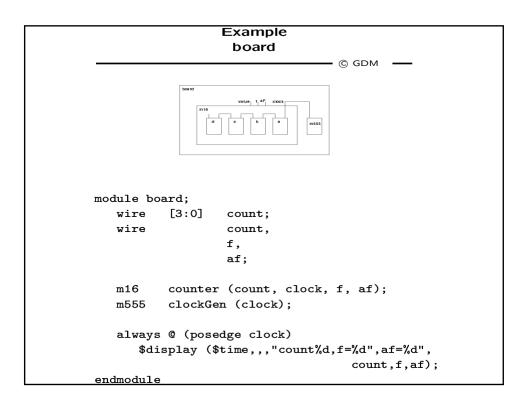

| Example<br>simulation                                                      |  |

|----------------------------------------------------------------------------|--|

|                                                                            |  |

| 5 count=x,f=x,af=x<br>100 count=1,f=0,af=0<br>200 count=2,f=0,af=0         |  |

| 300 count=3,f=0,af=0<br>400 count=4,f=0,af=0<br>500 count=5,f=0,af=0       |  |

| 600 count=6,f=0,af=0<br>700 count=7,f=0,af=0<br>800 count=8,f=0,af=0       |  |

| 900 count=9,f=0,af=0<br>1000 count=10,f=0,af=0<br>1100 count=11,f=0,af=0   |  |

| 1200 count=12,f=0,af=0<br>1300 count=13,f=0,af=0<br>1400 count=14,f=0,af=0 |  |

| 1500 count=15,f=1,af=1<br>1600 count=0,f=0,af=0<br>1700 count=1,f=0,af=0   |  |

| 1800 count=2,f=0,af=0<br>1900 count=3,f=0,af=0                             |  |

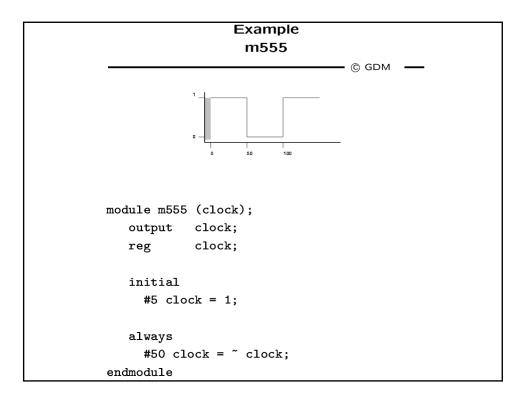

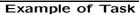

|            | Evan               | anlo                                     |

|------------|--------------------|------------------------------------------|

|            | Exan               | ipie                                     |

|            | mar                | k1                                       |

|            |                    |                                          |

|            |                    | © GDM                                    |

|            |                    |                                          |

|            |                    |                                          |

| module mai |                    |                                          |

| reg[31:    | :0] m[0:8191];     | //8192 x 32 bit memory                   |

| reg[12     | :0] pc;            | //13 bit program counter                 |

| reg[31:    | :0] acc;           | <pre>//32 bit accumulator</pre>          |

| reg[15:    | :0] ir;            | <pre>//16 bit instruction register</pre> |

| -          |                    | -                                        |

| always     |                    |                                          |

| begin      | 1                  |                                          |

|            | = m[pc];           |                                          |

|            | se (ir[15:13])     |                                          |

|            | b000: pc = m[ir[1] | 2:011:                                   |

|            | b0001: pc = pc + m |                                          |

|            | 'b010: acc = -m[ir |                                          |

|            | 'b011: m[ir[12:0]] |                                          |

|            |                    | - acc;                                   |

|            | 'Ъ100,             |                                          |

|            | 'b101: acc = acc - | ,                                        |

|            | 'b110: if(acc<0)pc | =pc+1;                                   |

| enc        | lcase              |                                          |

| pc=        | =pc+1;             |                                          |

| end        |                    |                                          |

| endmodule  |                    |                                          |

## Tasks and Functions

- Used in behavioral modeling

- task:

- equivalent to a software procedure

- function:

- equivalent to a software function

## Tasks and Functions

- A function executes in a time unit

- A task can contain time-controlling statements

- A function cannot enable a task

- A task can enable other tasks and functions

- A function must have at least one input argument

- A task may have zero or more arguments

- A function returns a single value

- A task does not return any value

| Example of Function                               |

|---------------------------------------------------|

| © CDM                                             |

| © GDM                                             |

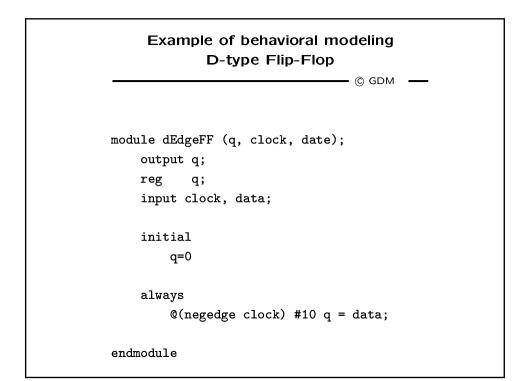

| module mark1Fun;                                  |

| //declarations as before                          |

|                                                   |

| always                                            |

| begin                                             |

| <pre>ir=m[pc];</pre>                              |

| case(ir[15:13]);                                  |

| //case expressions, as before                     |

| 3'b111: acc = multiply(acc, m [ir [12:0]]);       |

| endcase                                           |

| pc = pc + 1;                                      |

| end                                               |

|                                                   |

| function [31:0] multiply;                         |

| input [31:0] a;                                   |

| input [31:0] b;                                   |

| <pre>reg [15:0] mcnd,mpy;</pre>                   |

| log [loto] mond, mpy,                             |

| begin                                             |

| mpy =b[15:0];                                     |

| mcnd = a[15:0];                                   |

| multiply = 0;                                     |

| repeat (16)                                       |

| begin                                             |

| if (mpy[0])                                       |

| <pre>multiply = multiply + {mcnd,16'h0000};</pre> |

| <pre>multiply = multiply&gt;&gt;1;</pre>          |

| mpy = mpy >> 1;                                   |

| end                                               |

| end                                               |

| endfunction                                       |

|                                                   |

| endmodule                                         |

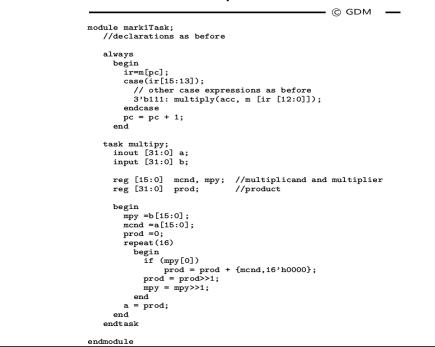

| Example                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------|

| © GDM                                                                                                              |

| <pre>module topNE();</pre>                                                                                         |

| wire [15:0] number, numberOut;                                                                                     |

| <pre>numberGenNE ng(number);<br/>fibNumberGenNE fng(number, numberOut);<br/>endmodule</pre>                        |

| <pre>module numberGenNE(number);<br/>output [15:0] number;<br/>reg [15:0] number;<br/>event ready</pre>            |

| <pre>initial   number = 3;</pre>                                                                                   |

| always<br>begin<br>#100 number=number + 1;<br>-> ready; //generate event signal<br>end                             |

| endmodule                                                                                                          |

| <pre>module fibNumberGenNE(startingValue, fibNum);     input [15:0] startingValue;     output [15:0] fibNum;</pre> |

| reg [15:0] myValue;<br>reg [15:0] fibNum;                                                                          |

| always                                                                                                             |

| begin                                                                                                              |

| <pre>@ng.ready //accept event signal myValue = startingValue</pre>                                                 |

| for (fibNum = 0; myValue !=0; myValue = myValue -1)                                                                |

| fibNum = fibNum + myValue;                                                                                         |

| <pre>\$display ("%d, fibNum=%d", \$time, fibNum); end</pre>                                                        |

| end<br>endmodule                                                                                                   |

|                     | Streng            | gth specifi                                      |                             | ом — ма                 |

|---------------------|-------------------|--------------------------------------------------|-----------------------------|-------------------------|

| Strength<br>Name    | Strength<br>Level | Element<br>Modeled                               | Declaration<br>Abbreviation | Printed<br>Abbreviation |

| Supply Drive        | 7                 | Power supply connection                          | supply                      | Su                      |

| Strong Drive        | 6                 | Default gate<br>and assign<br>output<br>strength | strong                      | St                      |

| Pull Drive          | 5                 | Gate and<br>assign output<br>strength            | pull                        | Pu                      |

| Large<br>Capacitor  | 4                 | Size of trireg<br>net capacitor                  | g large                     | La                      |

| Weak Drive          | 3                 | Gate and<br>assign output<br>strength            | weak                        | We                      |

| Medium<br>Capacitor | 2                 | Size of trireg<br>net capacitor                  | g medium                    | Me                      |

| Small<br>Capacitor  | 1                 | Size of trireg<br>net capacitor                  | g small                     | Sm                      |

| High<br>Impedance   | 0                 | Not<br>applicable                                | highz                       | Hi                      |

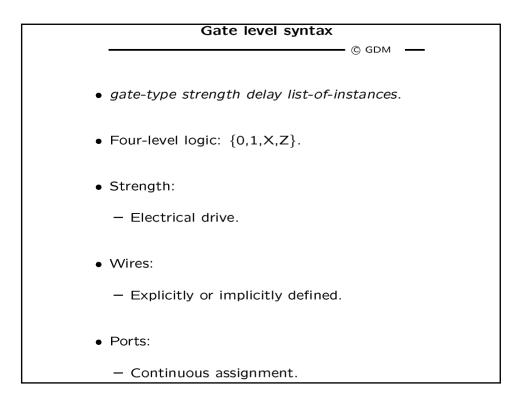

## Delay specification

– © GDM –

• Applies to gates, nets and c-assignments.

- #(rise , fall , dtoZ).

- Extensible to:

- Minimum, typical, maximum.

- Block delays:

- \* Delay paths through a block.

|               | Example                             |

|---------------|-------------------------------------|

|               | © GDM                               |

|               |                                     |

| module IOB    | uffer (bus, in, out, dir);          |

| inout         | bus;                                |

| input         | in, dir;                            |

| output        | out;                                |

| -             |                                     |

| paramet       | er                                  |

| 1             | = 3, $R_{Typ}$ = 4, $R_{Max}$ = 5,  |

|               | $= 3, F_Typ = 5, F_Max = 7,$        |

|               | $= 12, Z_{Typ} = 15, Z_{Max} = 17;$ |

| 2_1111        | $= 12, 2_1yp = 13, 2_max = 17,$     |

| <b>b</b> f:f1 | #(R_Min: R_Typ: R_Max,              |

| buiiii        |                                     |

|               | F_Min: F_Typ: F_Max,                |

|               | Z_Min: Z_Typ: Z_Max)                |

|               | (bus, out, dir);                    |

|               |                                     |

| buf           | #(R_Min: R_Typ: R_Max,              |

|               | F_Min: F_Typ: F_Max,                |

|               | (in, bus);                          |

|               |                                     |

| endmodule     |                                     |

|               |                                     |

```

Example

— © GDM –

module dEdgeFF (clock, d, clear, preset, q);

input clock, d, clear, preset;

output q;

specify

// specify parameters

specparam tRiseClkQ =100,

tFallClkQ =120,

tRiseCtlQ =50,

tFallCtlQ =60,

// module path declarations

(clock => q) = (tRiseClkQ, tFallClkQ);

(clear, preset *> q) = (tRiseCtlQ, tFallCtlQ);

endspecify

// description of module's internals

endmodule

```

|              | Example                            |

|--------------|------------------------------------|

|              | © GDM                              |

|              | <b>G</b> SPIN                      |

|              | rryX(carryOut, carryIn, aIn, bIn); |

| output car   | -                                  |

| input aIn    |                                    |

| bIn          |                                    |

| car          | rryIn;                             |

|              |                                    |

| table        | <b>A</b>                           |

| 0 00 :       |                                    |

| 0 01 :       |                                    |

| 0 10 :       |                                    |

| 0 11 :       |                                    |

| 1 00 :       |                                    |

| 1 01 :       |                                    |

| 1 10 :       |                                    |

| 1 11 :       |                                    |

| 0 0x :       |                                    |

| 0 x0 :       |                                    |

| x 00 :       |                                    |

| 1 1x :       |                                    |

| 1 x1 :       |                                    |

| x 11 :       | 1;                                 |

| endtable     |                                    |

| endprimitive |                                    |