| Georgia<br>Tech                                                                                                                                                                                               | Procedures: Placement                                                                |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|

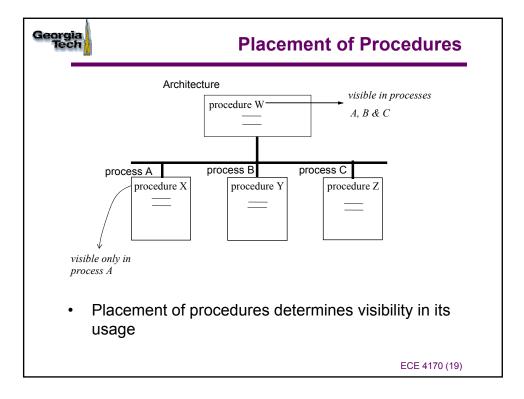

| architecture behavioral of cpu is<br><br>declarative region<br>procedures can be placed in th<br><br>begin<br>process_a: process<br>declarative region of a process<br>procedures can be placed here<br>begin | eir entirety here<br>visible to all<br>processes<br>visible only within<br>process a |  |  |

| <br>process body<br><br>end process_a;<br>process_b: process<br>declarative regions<br>begin<br>process body<br>end process_b;<br>end architecture behavioral;                                                | visible only within process_b                                                        |  |  |

|                                                                                                                                                                                                               | ECE 4170 (18)                                                                        |  |  |

## Georgia Tech

## **Concurrent Procedure Calls**

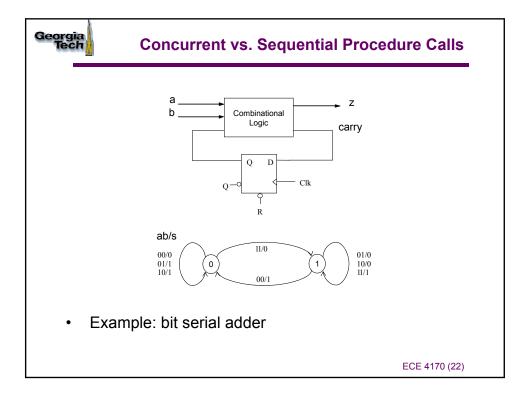

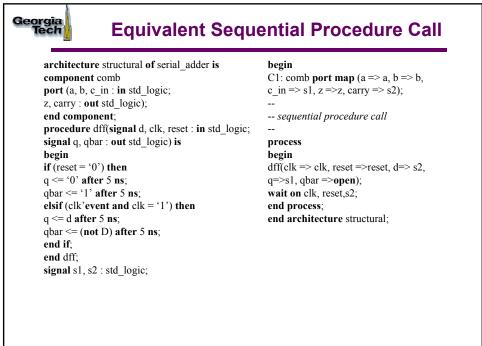

architecture structural of serial adder is component comb port (a, b, c\_in : in std\_logic; z, carry : **out** std logic); end component; procedure dff(signal d, clk, reset : in std\_logic; signal q, qbar : out std\_logic) is begin if (reset = (0)) then q <= '0' after 5 ns; qbar <= '1' after 5 ns; elsif (rising\_edge(clk)) then q <= d after 5 ns; qbar <= (not D) after 5 ns; end if; end dff; signal s1, s2 : std\_logic;

```

C1: comb port map (a => a, b => b,

c_in => s1, z =>z, carry => s2);

--

-- concurrent procedure call

```

dff(clk => clk, reset =>reset, d=> s2, q=>s1, qbar =>**open**); **end architectural** structural;

- · Variables cannot be passed into a concurrent procedure call

- Explicit vs. positional association of formal and actual parameters

ECE 4170 (23)

| Georgia<br>Tech                                                                                                                                                                                                                                                                                                                         | Visibility Rules                                                                        |                                                                                                                                                            |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                                                                                                                                                                                                                                                                                         | fîle.vhd                                                                                | library IEEE;<br>use IEEE.std_logic_1164.all;<br>entity design-1 is<br><br>library IEEE;<br>use IEEE.std_logic_1164.rising_edge;<br>entity design-2 is<br> |  |  |

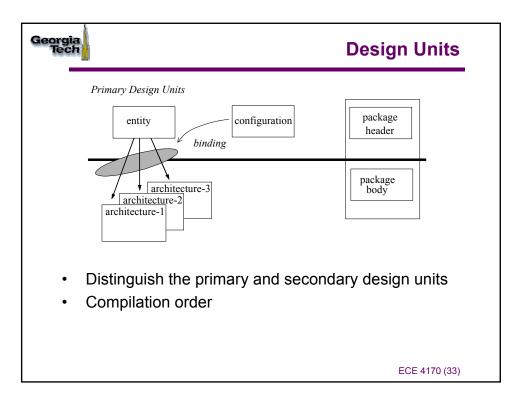

| <ul> <li>When multiple design units are in the same file visibility of libraries and packages must be established for each <i>primary</i> design unit (entity, package header, configuration) separately!         <ul> <li>Secondary design units derive library information from associated primary design unit</li> </ul> </li> </ul> |                                                                                         |                                                                                                                                                            |  |  |

| <ul> <li>The use clause may selectively establish visibility, e.g., only the function rising_edge() is visible within entity design-2</li> <li>Secondary design inherit visibility</li> </ul>                                                                                                                                           |                                                                                         |                                                                                                                                                            |  |  |

| •                                                                                                                                                                                                                                                                                                                                       | Note design unit descriptions are decoupled from file unit boundaries     ECE 4170 (34) |                                                                                                                                                            |  |  |