| Georgia<br>Tech                                                                                                                                                                                                                                                   | Revisit the Example                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| architecture behavior of inflate is<br>begin<br>process (x, y, z, sel) is<br>variable s1, s2: std_logic;<br>begin<br>w <= '0'; output signal set to a defau<br>if (sel = '1')then<br>s1:= x and z; body generates<br>s2:= s1 xor y;<br>w <= s2 and s1;<br>end if; | It value to avoid latch inference<br>s combinational logic |

| end process;<br>end architecture behavior;<br>x<br>z<br>y<br>sel                                                                                                                                                                                                  |                                                            |

|                                                                                                                                                                                                                                                                   | ECE 4170 (7)                                               |

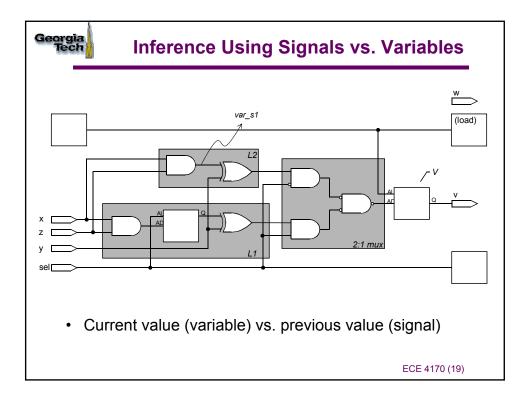

| Georgia<br>Tech Inference Using                                                                                                                                                                                                                                                                                      | g Signals vs. Variables                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| library IEEE;<br>use IEEE.std_logic_1164.all;<br>entity sig_var is<br>port (sel : in std_logic;<br>x, y, z: in std_logic;<br>v, w: out std_logic );<br>end entity sig_var;<br>architecture behavior of sig_var is<br>signal sig_s1 : std_logic;<br>begin<br>process (x, y, z, sel) is<br>variable var_s1: std_logic; | L1: if (sel = '1')then<br>sig_s1 <= x and z;<br>v <= sig_s1 xor y;<br>end if;<br>L2: if (sel = '0') then<br>var_s1 := x and z;<br>v <= var_s1 xor y;<br>end if;<br>end process;<br>end architecture behavior; |

| <ul> <li>Variable synthesized to a to a latch</li> <li>Why is a latch inferred at are covered?</li> </ul>                                                                                                                                                                                                            | wire vs. signal synthesized all since all execution paths                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                      | ECE 4170 (18)                                                                                                                                                                                                 |

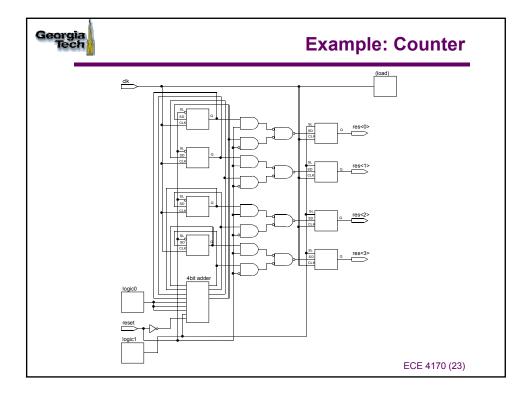

| Georgia<br>Tech | Example: Counter                                                                                                                                                                                        |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | entity counter is<br>port (clk, reset : in std_logic;<br>res : out unsigned (3 downto 0));<br>end entity counter;                                                                                       |

|                 | <pre>architecture behavior of counter is begin process (clk, reset) is variable var_count : unsigned (3 downto 0); begin if (rising_edge (clk)) then if (reset = '1') then res &lt;= "0000"; else</pre> |

|                 | ECE 4170 (22)                                                                                                                                                                                           |

| Georgia<br>Tech |             |                                                          | State     | Encodings     |

|-----------------|-------------|----------------------------------------------------------|-----------|---------------|

|                 | State       | Sequential                                               | Gray Code | One Hot       |

|                 | 0           | 000                                                      | 000       | 00000001      |

|                 | 1           | 001                                                      | 001       | 00000010      |

|                 | 2           | 010                                                      | 011       | 00000100      |

|                 | 3           | 011                                                      | 010       | 00001000      |

|                 | 4           | 100                                                      | 110       | 00010000      |

|                 | 5           | 101                                                      | 111       | 00100000      |

|                 | 6           | 110                                                      | 101       | 0100000       |

|                 | 7           | 110                                                      | 100       | 1000000       |

| •               | Goal: optin | rel constructs f<br>nize area or sp<br>it illegal states | beed      | ed encodings  |

|                 |             |                                                          |           | ECE 4170 (30) |