| Georgia<br>Tech                                                                                                                  | Useful Code Bloo                                              | cks: Testing Models |  |

|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------------|--|

| use STD.textic<br>use Work.clas<br>the package<br>entity checkin,<br>end checking;<br>architecture b<br>begin<br>use file 1/0 to | sio. <b>all</b> ;<br>classio has been compiled into the worki | king directory      |  |

|                                                                                                                                  |                                                               | ECE 4170 (14)       |  |

| Georgia<br>Tech | Example (cont.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | Example (cont.)<br>io_process: process this process performs the test<br>file infile : TEXT is in "infile.txt"; functions<br>file outfile : TEXT is out "outfile.txt";<br>variable uf : line;<br>variable msg : string(1 to 19) := "This vector failed!";<br>variable check : std_logic_vector (4 downto 0);<br>begin<br>while not (endfile (infile)) loop loop through all test vectors in<br>read_v1d (infile, check); the file<br>make assignments here<br>wait for 20 ns; wait for outputs to be available after applying<br>if (Q /= check (1) or (Qbar /= check(0))) then error check<br>write (buf, msg);<br>writeline (outfile, buf);<br>write_v1d (outfile, check);<br>end if;<br>end loop;<br>wait; this wait statement is important to allow the simulation to halt!<br>end process io_process;<br>end architectural behavioral; |

|                 | ECE 4170 (18)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

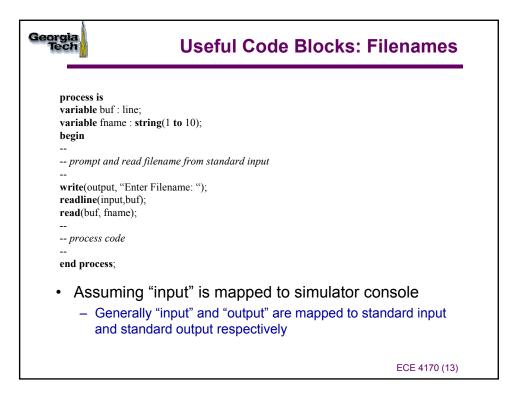

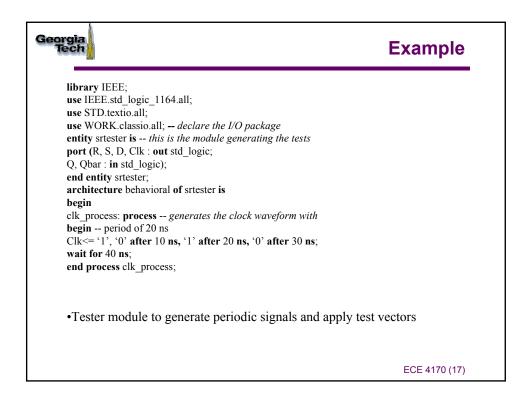

| library IEEE;                                                   |                                       |

|-----------------------------------------------------------------|---------------------------------------|

| use IEEE.std_logic_1164.all;                                    |                                       |

| use WORK.classio.all; declare the I/O package                   | ge                                    |

| entity srbench is                                               |                                       |

| end srbench;                                                    |                                       |

| architecture behavioral of srbench is                           |                                       |

| -                                                               |                                       |

| include component declarations here                             |                                       |

|                                                                 |                                       |

| configuration specification                                     |                                       |

| <br>6 T1 (1 1                                                   | · - 1)                                |

| for T1:srtester use entity WORK.srtester (beha                  | · · · · · · · · · · · · · · · · · · · |

| for M1: asynch_dff use entity WORK.asynch_d                     |                                       |

| signal s_r, s_s, s_d, s_q, s_qb, s_clk : std_logic;             |                                       |

| begin                                                           |                                       |

| T1: srtester <b>port map</b> (R=>s_r, S=>s_s, D=>s_c<br>s clk); | u, Q=>s_q, Qbar=>s_qb, Cik =>         |

| M1: asynch dff port map (R=>s r, S=>s s, D=                     | ->a d O=>a a Obar=>a ab Cllr          |

| => s clk);                                                      | ->s_a, Q->s_q, Qbai->s_qb, Cik        |

| end behavioral;                                                 |                                       |

| enu benaviorai,                                                 |                                       |