| Georgia                                                                                                                                                                                                                                                                            | For Hardware Generation      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

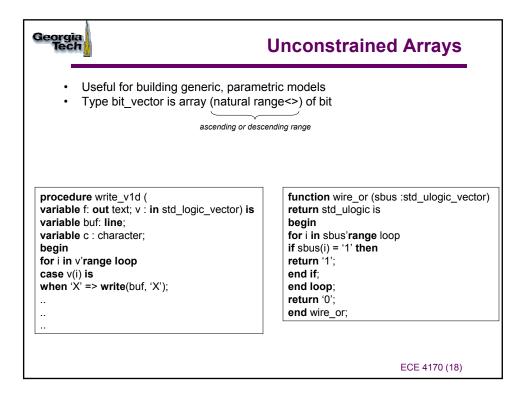

| library IEEE;<br>use IEEE.std_logic_1164.all;<br>entity gregister is<br>port (din : in std_logic_vector;<br>qout: out std_logic_vector;<br>clk, we : in std_logic);<br>end entity gregister;                                                                                       |                              |

| architecture behavioral of gregister is                                                                                                                                                                                                                                            | unconstrained arrays         |

| component dff_en is<br>Port ( d : in STD_LOGIC;<br>we : in STD_LOGIC;<br>clk : in STD_LOGIC;<br>q : out STD_LOGIC);<br>end component dff_en;<br>begin<br>dreg: for i in din'range generate<br>reg: dff_en port map( d=>din(i), q=><br>end generate;<br>end architecture behavioral | >qout(i), we=>we, clk=>clk); |

|                                                                                                                                                                                                                                                                                    | ECE 4170 (19)                |

| Georgia<br>Tech                                                                                                                               | Record Types                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| distinct type                                                                                                                                 | (17 <b>downto</b> 0);                                                                                               |

| type r_format is record<br>op : opcode;<br>dest: reg_addr;<br>source1 : reg_addr;<br>source2: reg_addr;<br>misc_op: op_format;<br>end record; | type i_format is record<br>op : opcode;<br>dest: reg_addr;<br>source1 : reg_addr;<br>mem_addr: addr;<br>end record; |

| op dest source1 source2 op_for                                                                                                                | mat op dest source1 mem_addr                                                                                        |

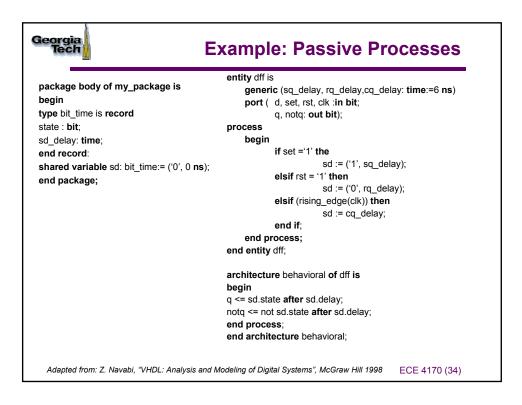

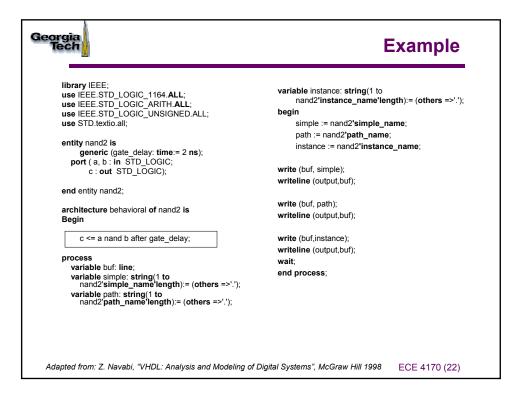

## Example

entity dff is generic (sq\_delay, rq\_delay,cq\_delay: time:=6 ns) port (d, set, rst, clk :in bit; q, notq: out bit); end entity dff;

architecture behavioral of dff is begin process (rst, clk, set) type bit\_time is record state : bit; sd\_delay: time; end record: variable sd: bit\_time:= ('0', 0 ns);

## begin

if set ='1' the

sd := ('1', sq\_delay);

elsif rst = '1' then

sd := ('0', rq\_delay);

elsif (rising\_edge(clk)) then

sd := cq\_delay;

end if;

q <= sd.state after sd.delay; notq <= not sd.state after sd.delay; end process; end architecture behavioral;

Adapted from: Z. Navabi, "VHDL: Analysis and Modeling of Digital Systems", McGraw Hill 1998 ECE 4170 (33)