| Timetest, 3 <sup>rd</sup> try                                                                                                |                                                                                                                                                   |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

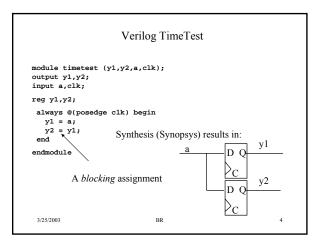

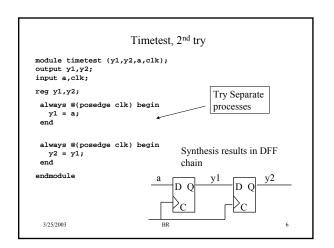

| <pre>module timetest (y1,y2,a,clk) output y1,y2; input a,clk; reg y1,y2; always @(posedge clk) begin    y1 = #1 a; end</pre> | Delays are added. Note that<br>the delays are added on the<br>right hand side, in front of<br>the 'a' signal. This means<br>that the 'a' value is |  |  |  |

| always @(pogedge clk) begin<br>y2 = #1 y1;<br>end<br>endmodule                                                               | sampled on the rising edge,<br>but the assignment is<br>delayed by 1 time unit, and<br>so simulates a clock-to-q<br>delay.                        |  |  |  |

| Synthesis results in DFF chain.<br>3/25/2003 BR 8                                                                            |                                                                                                                                                   |  |  |  |

|                                                                                                                                                                                               | Some Rules                                              |                                                                                                 |   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------|---|

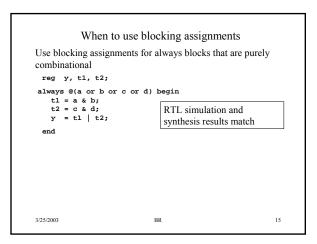

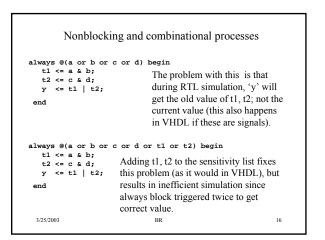

| <ul> <li>Verilog in which gate level simulat are:</li> <li>Use blocking ass combinational</li> <li>Use only nonblog purely sequential sequential assign</li> <li>If you understand</li> </ul> | the differences between bi<br>nments in terms of simula | n synthesized<br>of these rules<br>are purely<br>cks that are either<br>onal and<br>locking and | 1 |

| 3/25/2003                                                                                                                                                                                     | BR                                                      | 17                                                                                              |   |

| A Subtle Error if using blocking assignments for sequential logic                                    |                                                                                                                                                    |  |  |

|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <pre>module dff (q,a,clk);<br/>output q;<br/>input a,clk;</pre>                                      | <pre>module dff (q,a,clk);<br/>output q;<br/>input a,clk;</pre>                                                                                    |  |  |

| reg q;                                                                                               | reg q;                                                                                                                                             |  |  |

| always @(posedge clk) begin<br>q = #1 a;<br>end<br>endmodule                                         | always @(posedge clk) begin<br>#1 q = a;<br>end<br>endmodule                                                                                       |  |  |

| Correct DFF simulation, 'a'<br>sampled on rising edge,<br>assigned 1 time unit after<br>rising edge. | Delays 1 time unit after<br>rising edge, then samples 'a'<br>value, and assigns this to 'q'.<br>This is modeling <i>negative</i><br>setup time!!!! |  |  |

| 3/25/2003                                                                                            | BR 18                                                                                                                                              |  |  |