### Type Definition Examples

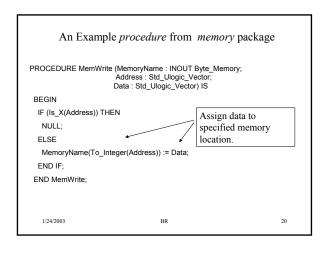

utilities directory has a package called memory that defines types/functions/procedures that are useful for memory modeling

TYPE Bit Memory IS ARRAY (Natural RANGE <>) OF Std Ulogic; TYPE Nibble Memory IS ARRAY (Natural RANGE <>) OF Std Ulogic Vector(3 DOWNTO 0); TYPE Byte\_Memory IS ARRAY (Natural RANGE <>) OF Std\_Ulogic\_Vector(7 DOWNTO 0); TYPE Word\_Memory IS ARRAY (Natural RANGE <>) OF Std\_Ulogic\_Vector(15 DOWNTO 0);

TYPE LongWord Memory IS ARRAY (Natural RANGE <>) OF Std Ulogic Vector(31 DOWNTO 0);

1/24/2003 BR

### Multi-dimensional Array

This is an example of a multi-dimensional array type declaration.

TYPE Byte Memory IS ARRAY (Natural RANGE <>) OF Std Ulogic Vector(7 DOWNTO 0);

unconstrained

constrained

2

Only one array index range can be unconstrained:

i.e. "Natural Range <> "

The other ranges must be constrained. Would be illegal to define the

TYPE A\_Memory IS ARRAY (Natural RANGE <>) OF Std\_Ulogic\_Vector(Natural RANGE <>);

1/24/2003 BR

## Array Assignments

When assigning one array to another, the slice size must be the same as well as the data type.

TYPE Byte\_Memory IS ARRAY (Natural RANGE <>) OF Std\_Ulogic\_Vector(7

TYPE Word\_Memory IS ARRAY (Natural RANGE <>) OF Std\_Ulogic\_Vector(15 DOWNTO 0):

variable a\_mem: Byte\_Memory(0 to 1023); variable b\_mem: Byte\_Memory(0 to 2047); variable c\_mem : Word\_Memory (0 to 511);

legal, slice size is the same. a\_mem (3 to 10) := b\_mem (11 to 18); illegal, slice size is different. a\_mem (20 to 30) := b\_mem (20 to 40);

elements are different c\_mem(2) := a\_mem (2);

1/24/2003

### RECORD types

A record type is a composite object type whose elements are named:

type myrec is record some\_real: real; some\_int: integer; a string: string (1 to 5);

a\_bool: boolean; end record;

Usage example:

variable tmp; myrec;

$tmp.some\_real := -30.4$ tmp. some\_int := 10; tmp.a\_string := "Hello";

tmp.a\_bool := TRUE; Signals can be record types!!! Can be helpful for complex modeling.

Assigning Default Values to a Record Type

type myrec is record some\_real: real; some\_int: integer; Positional assignment string (1 to 5): a\_string: (order is same as in a bool: boolean: record declaration) variable tmp: myrec := (1.0, -1, "hello", TRUE)

OR variable tmp: myrec := (some\_int => -1, a\_string => "hello". some\_real => 1.0

Using a name list, order is not important because record field names are used for assignment

1/24/2003 BR

a\_bool => FALSE);

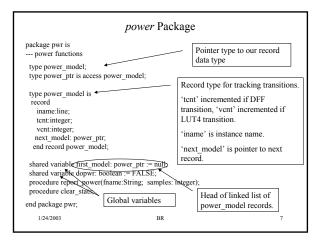

**Example: Tracking Transition Counts**

Signal transition counts are useful in gate-level simulations for power estimation programs.

Each signal transition consumes power.

Transient computations (transient gate level switching) can be a large source of power consumption in some cases.

Problem: Have a netlist that has D-flip flops (DFFs) + LUT4 (4input lookup tables).

- 1. Would like to track the total number of signal transitions over a period of time.

- 2. Would like to distinguish between DFF and LUT4 transitions.

1/24/2003 BR

### Global Variables

- A variable can be declared outside of a procedure, function or process only if it is declared as shared

- Will make this variable visible to all procedures, functions,

- · Useful for keeping track of statistics, global data structures

- · Must remember: cannot predict the order in which a global variable will be updated if multiple processes update it, and the processes are all triggered by the same

- Order of process execution for simultaneous event triggering is simulator dependent

1/24/2003 BR

## Modeling Approach

- At startup, each instance in our netlist will create a record of type 'power model'.

- Insert this into a linked list of all such power\_model records

- A global shared variable will be used to point to the head of this linked list

- · Each time a signal transition occurs on an input, increment a counter in the power model

- For DFFs, increment 'tent'

- For LUT4s, increment 'vcnt'.

- · Can enable/disable transition counter via a global variable called donwr

- Only increment transition counts if this variable is TRUE

- · Print transition stats using 'report\_power' procedure

- Clear stats using 'clear\_stats' procedure

1/24/2003

#### library ieee; use ieee.std logic 1164.all; dfr model library power; use power.pwr.all; 'new' allocates new record architecture a of dfr is structure. begin process(clk2,rst3) variable model: power ptr := null; 'instance name returns simulator dependent name if (model = null) then model := new power\_model'( new string'(a'instance\_name), 0, 0, first\_model); first\_model := model; link into list of all such end if: record structures if (rst3 = '0') then q <= transport '0' after gdelay; elsif (clk2'event and clk2 = '1') then q <= transport data1 after gdelay; - increment tent of DFFs for EVERY clock edge if (dopwr = TRUE) then model.tcnt := model.tcnt + 1; end if: dopwr true if statistics keeping end if; turned on, increment transition end process; count end a; 1/24/2003

### Other Comments

The code below allocates the new record structure and links into the global list.

```

process(clk2,rst3)

variable model: power_ptr := null;

begin

if (model = null) then

model := new power_model'( new string'(a'instance_name), 0, 0, first_model); first_model := model;

```

Note that we have no guarantee of what order the processes corresponding to the DFRs/LUT4s are initially executed in so there is no particular order of the power records on the global linked list.

The code is executed only once since 'model' will be non-null afterwards. The initial value of 'first-model' global variable is null, so last record will have a 'next model' value of NULL.

1/24/2003 BR 11

```

'instance name Attribute

process(clk2,rst3)

variable model: power_ptr := null;

if (model = null) then

model := new power_model'( new string (a'instance_name) 0, 0, first_model);

first_model := model;

"a" is the architecture name of this entity.

a'instance name returns a simulator dependent string that

describes the hierarchical path from the root of the design

```

heirarchy down to this component architecture.

'instance name can be used with anything other than local ports or generics of a component declaration.

1/24/2003 12

```

LUT4 Entity

library IEEE; use IEEE.std_logic_1164.all;

entity lut4 is

generic (

gdelay: time := 5 ns:

fmap: std_logic_vector(15 downto 0):= "XXXXXXXXXXXXXXXXX");

port( A, B, C, D : in std logic; O : out std logic);

end lut4:

LUT4 is a 4-input LookUp table (such as used in Xilinx, Altera

FPGAs).

Equivalent to a 16 x 1 SRAM (inputs A,B,C,D are address lines

where A is MSB, D is LSB).

Generic 'fmap' used to specify contents of LUT4.

1/24/2003

BR

13

```

```

library IEEE; use IEEE.std_logic_1164.all;

library power;use power.pwr.all;

LUT4 Architecture

architecture a of lut4 is

beain

process (A,B,C,D)

variable index, lastval:integer;

variable lasttrig: time := 0 ns

variable model: power ptr := null:

begin

if (model = null) then

model := new power_model'( new string'(a'instance_name),0, 0, first_model);

first_model := model;

Compute LUT4 address

end if:

index := 0;

if (A = '1') then

Only count transition if

index := index + 8;

end if;

if (B = '1') then

index := index + 4;

current address is different

if (C = '1') then

index := index + 2;

end if;

if (D = '1') then

from last address. Filter

index := index + 1;

O <= transport fmap(index) after gdelay;

spikes < 1 ns.

if (lastval /= index and ((now - lasttrig) > 1 ns)) then

if (dopwr = TRUE and (not nopower)) then

model.vcnt := model.vcnt + 1;

end if;

lastval := index; lasttrig := NOW;

end if;

end process

BR

14

end a:

```

# Traversing the Record List

*clear\_stats* procedure is used to zero out statistics after recording some signal transitions.

```

procedure clear_stats is

variable head_ptr: power_ptr;

begin

head_ptr := first_model;

while head_ptr /= null loop

head_ptr.vent :=0;

head_ptr.vent :=0;

head_ptr.vent :=0;

head_ptr.vent :=0;

end loop;

end;

report_power procedure traverses list in a similar fashion

except it sums the transition counts and prints out values to

screen

```

### Comments on Packages Packages consists of a package declaration and a package body. Any subprogram (function, procedure) or variable that is to be public to users of this package must be in the declaration. If an element is not in the declaration but is in the body, then the element can only be used by other elements in the body - it is not 'visible' externally of the body. package test is Public function foo (a: integer) return integer; CONSTANT aconst: real := 3.14; end test; package body test is CONSTANT PCONST: integer := -1; Private function foo (a: integer) is begin foo implementation in return ((a+1) \* PCONST); package body

end foo; end test; 1/24/2003

### Package Dependencies

- If an entity/package/configuration uses a package, and that package declaration is changed, then must recompile the the entity/package/configuration that uses the package

- If only package body changes, then don't have to recompile as long as package declaration and package body are in different files.

- The value of a CONSTANT does not have to be specified in the package declaration:

```

package test is

CONSTANT PI: real;

end test;

package body test is

CONSTANT PI: real := 3.14159;

end test;

```

1/24/2003

Called a *deferred* constant. Can change this value without having to recompile dependent packages, entities, configurations.

1/24/2003 BR 17

#