#### VHDL Simulation Environment

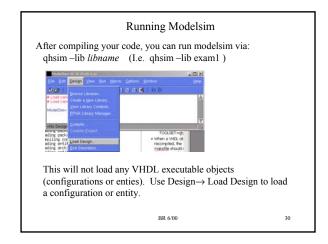

We will use the *modelsim* environment for both VHDL and Verilog simulation in this class.

I will provide a directory structure + Makefiles that will work with the *modelsim* software on the UNIX machines.

A free version of the *modelsim* software for Window-based PCs is available, you can copy the file:

http://www.ece.msstate.edu/~reese/tmp/webpack\_mxe\_simulator.exe

There are some code-size limitations with the free version, but all of the early labs seem to work ok with it.

BR 6/00

#### Compiling Using a Makefile

To compile the contents of a library using one of the Makefiles, change directories to the 'src' directory and do:

swsetup modelsim gmake -f Makefiles/Makefile.exam1 TOOLSET=qhdl

This will compile the contents of the 'exam1' library. The Makefile has been written to be compatible with several VHDL simulators, hence the use of the 'TOOLSET' variable.

The 'swsetup' command only has to be issued once in order to put the Mentor QHDL tools on your path; you may want to add this to your .cshre file.

BR 6/00

4

| Directory Structure                                                                                                                                                                                            |   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Grab the zip archive at:<br>http://www.ece.msstate.edu/~reese/EE8993/vhdl_course.zip                                                                                                                           |   |

| Unpack this with: 'unzip vhdl_course.zip'.                                                                                                                                                                     |   |

| This will setup a directory structure that looks like:                                                                                                                                                         |   |

| vhdl_course/src/<br>/Makefiles Makefiles for VHDL libraries<br>/exam1 source directory for VHDL example #1<br>/utilities various files that define useful<br>VHDL packages which we will use in<br>this course |   |

| vhdl_course/obj/qhdl/<br>/exam1 compiled VHDL object code for example #1<br>/utilities compiled VHDL object code for utilities                                                                                 |   |

| BR 6/00                                                                                                                                                                                                        | 2 |

#### Makefiles

Except for the 'Makefiles' directory, each directory under the 'src' directory represents a VHDL 'library'.

The VHDL files within the library contain VHDL entities, packages, and configurations that reside within the library.

Under the 'Makefiles' directory, there is a 'Makefile' for each VHDL library, i.e:

src/Makefiles/Makefile.exam1 - makefile for library 'exam1' src/Makefiles/Makefile.utilities - makefile for library 'utilities'

BR 6/00

3

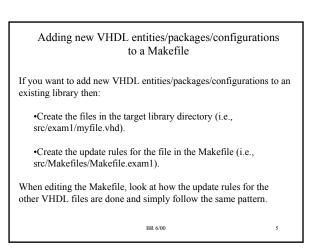

Adding a new library

If you want to add your own VHDL library, then follow these steps, all of which must be executed from within the 'src/' directory:

• Create the new library directory mkdir mylib

•Create the QHDL library object directory via: qhlib ../obj/qhdl/mylib mkdir ../obj/qhdl/mylib/ts

The result of this command will be a new directory '../obj/qhdl/mylib' which will have some QHDL setup files in it. The 'ts' directory holds timestamp information required by our Makefile setup.

BR 6/00

#### Adding a new library (cont)

•Create a logical to physical name mapping for the new library via: qhmap mylib ../obj/qhdl/mylib

This command edits the 'src/modelsim.ini' file and adds a logical to physical name mapping entry. You could also simply edit the src/modelsim.ini file manually.

•Create a 'Makefiles/Makefile.mylib' makefile that will handle the compilation of any VHDL files in 'mylib'. You can copy one of the other library Makefiles and edit it

BR 6/00

7

8

9

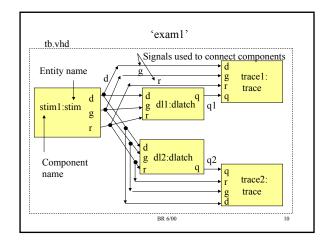

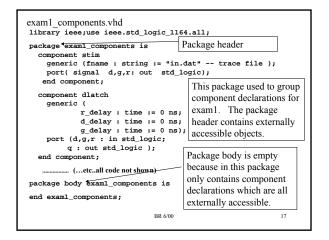

### src/exam1 Files

The 'src/exam1' directory contains the following files:

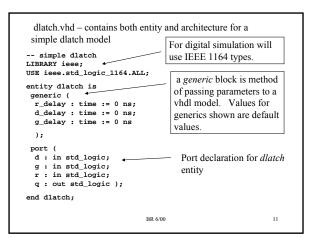

•dlatch.vhd - VHDL entity and architecture of simple D latch

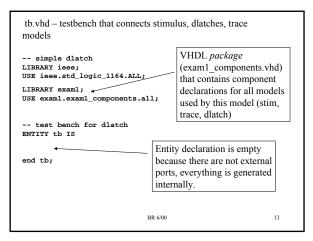

•tb.vhd - VHDL entity and architecture of a test bench which instantiates two latches, a stim component, and a trace component.

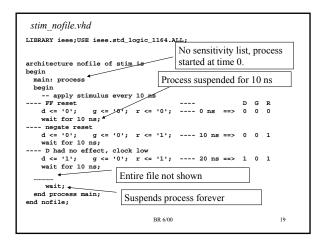

stim.vhd - VHDL entity of a stimulus module for the testbench

stim\_nofile.vhd - architecture for 'stim' which hardcodes testvectors

stim\_readfile.vhd - architecture for 'stim' which reads testvectors from file

trace.vhd - VHDL entity of a trace module for the testbench

cfg\_tb.vhd - VHDL configuration for the testbench which specifies uses the 'nofile' architecture for 'stim'.

•cfg\_tb2.vhd - VHDL configuration for the testbench which specifies uses the 'readfile' architecture for 'stim', plus a different set of generics for the latch delays.

BR 6/00

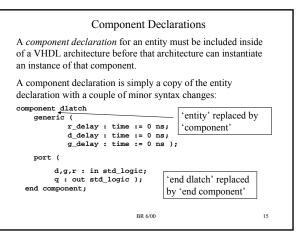

#### Some VHDL Vocabulary

- entity specifies the interface (inputs/outputs/generics) to a module

- architecture code that specifies the behavior of a module

- There can be more than architecture for an entity

- Each architecture would specify some different implementation (I.e., behavioral, RTL, gate level, etc).

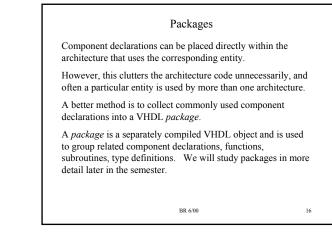

- *configuration* specifies the entities, generics, architectures to use for components within a particular model

- package a collection of VHDL type definitions, procedures, functions, and component declarations.

- *library* a collection of entities, architectures, configurations, packages

BR 6/00

architecture behv of dlatch is Sensitivity list - process begin process (d,g,r) triggered on any event on begin these signals if (r = '0') then -- reset went low q <= transport '0' after r\_delay;</pre> elsif (g = '1') then -- changes can only occur on output when g is '1' -- see if event occurred on either g or d -- ignore otherwise if (g'event) then -- just went to a one, schedule the event q <= transport d after g\_delay; end if: Delay specification if (d'event) then in VHDL -- change on d, schedule change q <= transport d after d\_delay; end if; end if; end process; end behv; BR 6/00 12

| architecture A of tb is<br>signal d,g,r: std_logic;<br>signal q1,q2: std_logic;                                                                                                                                                                |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <pre>begin<br/>stim1:stim<br/>port map ( d =&gt; d, g =&gt; g, r =&gt; r);</pre> Component instantiation<br>component name first, then entity name                                                                                             |  |  |

| <pre>dl1 : dlatch   port map ( d =&gt; d, g =&gt; g, r =&gt; r, q =&gt; ql);</pre>                                                                                                                                                             |  |  |

| tracel: trace<br>port map ( d => d, g => g, r => r, q => ql);                                                                                                                                                                                  |  |  |

| dl2 : dlatch<br>port map ( d => d, g => g, r => r, q => q2);                                                                                                                                                                                   |  |  |

| <pre>trace2: trace port map ( d =&gt; d, g =&gt; g, r =&gt; r, q =&gt; q2); end; Port map shows how ports connect to signals     port_name =&gt; signal_name     If two ports connect to same signal, ports are connected.     BR 600 14</pre> |  |  |

| <i>stim.vhd</i> – entity for stimulus which provides inputs for dlatches.                   |  |  |

|---------------------------------------------------------------------------------------------|--|--|

| LIBRARY ieee;USE ieee.std_logic_1164.ALL;                                                   |  |  |

| stim for dlatch<br>ENTITY stim IS<br>generic (                                              |  |  |

| <pre>fname : string := "in.dat" trace file );</pre>                                         |  |  |

| port(                                                                                       |  |  |

| <pre>signal d,g,r: out std_logic );</pre>                                                   |  |  |

| end stim;                                                                                   |  |  |

| <i>stim_nofile</i> .vhd contains architecture that has input values hardcoded in vhdl file. |  |  |

| stim_readfile.vhd contains architecture that reads input<br>value from external file        |  |  |

| BR 6/00 18                                                                                  |  |  |

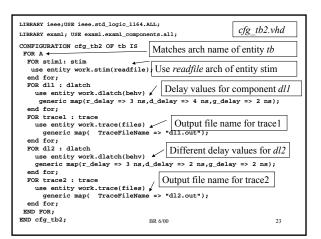

| LIERARY ieee;USE ieee.std_logic_1164.ALL;<br>LIERARY examl; USE examl.examl_components.all;                                                                      |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CONFIGURATION cfg_tb oF tb IS<br>FOR A + FOR stiml: stim                                                                                                         |  |  |  |

| use entity work.stim(nofile); Use <i>nofile</i> arch of entity stim<br>end for;<br>FOR dll: dlatch                                                               |  |  |  |

| <pre>FOR dl1 : dlatch use entity work.dlatch(behv) / Delay values for component dl1 generic map(r delay =&gt; 3 ns,d delay =&gt; 4 ns,g delay =&gt; 2 ns);</pre> |  |  |  |

| end for;<br>FOR tracel : trace                                                                                                                                   |  |  |  |

| <pre>use entity work.trace(files) Ultput file name for tracel generic map( TraceFileName =&gt; "dll.out"); end for;</pre>                                        |  |  |  |

| FOR dl2 : dlatch<br>use entity work.dlatch(behv)                                                                                                                 |  |  |  |

| <pre>generic map(r_delay =&gt; 3 ns,d_delay =&gt; 2 ns,g_delay =&gt; 2 ns);<br/>end for;</pre>                                                                   |  |  |  |

| FOR trace2 : trace<br>use entity work.trace(files)                                                                                                               |  |  |  |

| <pre>generic map( TraceFileName =&gt; "dl2.out"); end for;</pre>                                                                                                 |  |  |  |

| END FOR;<br>END cfg_tb; BR 6/00 22                                                                                                                               |  |  |  |

## Other Entities/Architectures • *stim\_readfile.vhd* • VHDL architecture that reads test vectors from a file – we will cover file I/O in a later lecture • *trace.vhd* • VHDL entity/architecture that tracks changes on dlatch component inputs/outputs and write these to a file • Typically want to write vector outputs to a file so that you can compare against a 'golden' file to see if the results match expected results.

BR 6/00

20

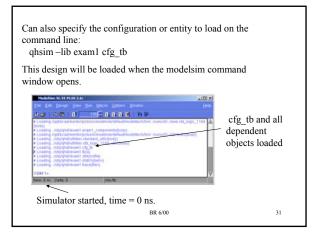

#### VHDL Configurations

A VHDL *configuration* can be used to select entities/architectures/generics for components within an architecture.

In this case, want to choose delay values for *dlatch* components and architecture for the stim entity (either architecture *nofile* or architecture *readfile*.

Configuration *cfg\_tb.vhd* uses the nofile architecture for the *stim* entity and a particular set of delay values for the dlatch components.

Configuration  $cfg\_tb2.vhd$  uses the *readfiles* architecture for the *stim* entity and the same delay values as used in  $cfg\_tb.vhd$ .

Can have more than one configuration for an architecture. A configuration is not required for an architecture.

BR 6/00

#### Makefile.exam1 (cont.) Recompilation Rules for Modelsim If an architecture is changed, must recompile that architecture. # Package exam1 components ## NOTE dependency on 'stim', 'trace', and 'dlatch' entities If architecture and entity are in separate files, then only have to \${LIB OBJ}/\${TS}/exam1 components.vhd: recompile the architecture file, not the entity file. \${LIB\_SRC}/exam1\_components.vhd \${LIB\_OBJ}/ts/stim.vhd \${LIB\_OBJ}/ts/trace.vhd \${LIB\_OBJ}/ts/dlatch.vhd If architecture and entity are in the same file, then recompiling the \${COMPILER} architecture, also recompiles the entity. This means that Modelsim \${TOUCH} now thinks the entity has changed, so any architectures that use that Note that the list of dependencies for the entity (or packages with component declarations for that entity) must exam1\_components.vhd timestamp says to recompile also be recompiled. exam1\_components if the source file (exam1\_components.vhd) To have minimum recompilation and clear dependency rules should changes or if any of the timestamps for stim, trace, and dlatch put each VHDL object in a separate file are updated. (entities/architectures/configurations in separate files, package The latter is needed because the *exam1\_components* package headers/bodies in separate files). contains the component declarations for stim, trace, and dlatch How you arrange VHDL objects and files is up to you! and this must be recompiled if these entities are recompiled. BR 6/00 28 25

BR 6/00

# Last Word on Makefiles

- · You can look at Makefile.exam1 and see how the other dependencies were done

- · How you group VHDL objects (entities, architectures, package headers, package bodies, configurations) into files will determine how you set your dependency rules.

- · These makefiles are only compatible with Gnu make program ('gmake'). They are not compatible with the normal Unix make ('make').

BR 6/00

#### 29

|                                                                                                                                              | Makefile.exam1                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| <pre>## ifeq (\${TOOLSET}, <u>ghd1) Compiler ccc</u> compiler e qvhcom \${DEBUG} \${LIBS} -33 - DEBUG = LIBS = -work \${LIB_OBJ} endif</pre> | ommand for modelsim<br>source \$<<br>Use VHDL 93 syntax        |

| <pre># This is the dummy directory for the time<br/>TS = ts<br/>TOUCH = touch \$@</pre>                                                      | tamp command Library name                                      |

| cfg_tb2 exam1_components<br>dlatch: \${LIB OBJ}/\${TS}/dlatch.vhd } 'al                                                                      | ll' is default target – will<br>ecute rules for all targets    |

| 1 5                                                                                                                                          | dlatch.vhd<br>dlatch.vhd changes, then<br>l update timestampe. |

Makefiles

- · Makefiles use to control recompilation of VHDL objects - Dependencies can be used in Makefiles to trigger recompilation of an object if another object changes

- Our approach is to use a separate Makefile for each VHDL library

- This does not handle dependencies between libraries, but should not encounter this problem very much

- · Our makefile template assumes source files reside in 'src/libname', and object files in 'obj/toolset/libname

- The libname is used to select a particular VHDL compiler for Modelsim use TOOLSET=qhdl

- When a VHDL object is recompiled, the makefile should update a timestamp for that object under 'obj/toolset/libname/ts/filename' where filename is the file that contained the VHDL object.

- This timestamp can be used to trigger recompilation of a dependent object.

BR 6/00

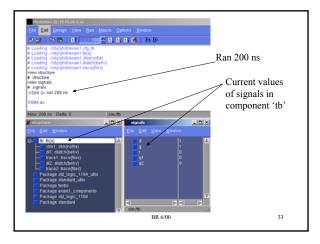

Can add signals to waveform window clicking on a signal in the *signals* window, then use:

$\mathrm{View} \rightarrow \mathrm{Wave} \rightarrow \mathrm{Selected} \ \mathrm{Signal}$

Click on objects in the structure window to change the currently displayed *signals* in the signals window.

After adding a signal to the wave window, you will not see a waveform until you either run the simulation for more time, or restart the simulation and run it again:

| VSIM > restart - f | -f option keeps currently |

|--------------------|---------------------------|

| VSIM > run 200 ns  | displayed signals         |

| BR 6/00            | 34                        |

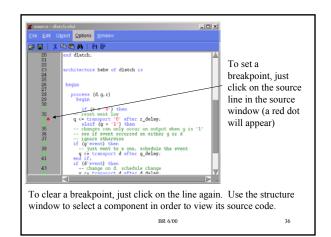

#### Modelsim Debugging Windows

- You can open different debugging windows via the 'View' menu

- The most useful ones are:

- Structure displays object structure of design. Selecting an object will change contents of source, signals windows

- Source displays source code of currently selected object

- $\ Signals-displays \ signals \ of \ currently \ selected \ object$

- Wave display waveforms of selected signals

- Variables display variable values of currently executing process

- When debugging, should always at least have structure, source, signals and wave windows open

BR 6/00

32

Once you have a desired set of signals displayed, use the File  $\rightarrow$  Save Format

to an external command file (such as 'exam1.do')

If you have your wave format saved to an external file (such as exam1.do), you can easily display these signals again when you execute the simulator via:

VSIM> do exam1.do

This will execute the commands in the file 'exam1.do'.

BR 6/00

#### Modelsim Misc. Comments

- You can single step code via the  $\text{Run} \rightarrow \text{Step}$  menu

- These debugging facilities are very powerful you should be able to determine exactly what your code is doing.

- If you want picosecond resolution instead of nanosecond resolution, you have to edit the modelsim.ini and change 'Resolution = ns' to 'Resolution = ps'.

Inhibts GUI window from appearing (command line interface only)

BR 6/00