For:reese

Printed on:Tue, Mar 23, 1999 08:04:25

**Document:Test 2**

Last saved on:Mon, Feb 23, 1998 15:46:48

Test #2 – EE 4743 – Spring 1998

My Name is: \_\_\_\_\_

You have 50 minutes to complete this test. Good luck! Point values for "sub-questions" are indicated inside parentheses.

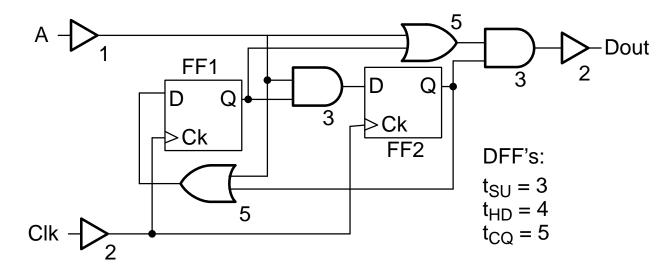

1. (30 points) Consider the diagram and answer the questions below. Delays for each gate are shown, in ns, next to each gate and delays for the flip–flops are shown in the table.

a. What is the longest register-to-register path? Based on that path, what is the fastest allowable clock cycle time?

b. What is the clock-to-output delay of Dout? Don't forget to consider both possible paths!

c. True or false: The propagation delay of a flip–flop from D to Q is a very important circuit parameter. Why?

2. (35 points) Consider the equation below.

$$Y = 0.5 Y@1 + 0.5 X - X@1$$

- a. Convert the equation to "shift-and-add" format.

- b. Draw a flowgraph for it. Assume shifts are combinational.

- c. What is the critical path? \_\_\_\_\_ The iteration loop critical path? \_\_\_\_\_

- d. Use pipelining to reduce the critical path so that it is maximally pipelined. For maximum credit, use a *minimal* number of pipeline stages.

|   | Number of Add                                                                                                                                                                | ers: N                                                                                                                            | Tumber of Shifters:        |                        |  |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------|--|

|   | •                                                                                                                                                                            | ints) Consider the flowgraph you drew in question 2b (the <i>non-pipelined</i> flowgraph that mented the equation in question 2). |                            |                        |  |

| г | Assign TASAP and TALAP pairs to the flowgraph. Assume the number of clock cycles per sample period equals the critical path. (Hint: You may want to redraw the graph below.) |                                                                                                                                   |                            |                        |  |

|   |                                                                                                                                                                              |                                                                                                                                   |                            |                        |  |

|   |                                                                                                                                                                              |                                                                                                                                   |                            |                        |  |

|   |                                                                                                                                                                              |                                                                                                                                   |                            |                        |  |

|   |                                                                                                                                                                              |                                                                                                                                   |                            |                        |  |

|   |                                                                                                                                                                              |                                                                                                                                   |                            |                        |  |

|   |                                                                                                                                                                              |                                                                                                                                   |                            |                        |  |

|   |                                                                                                                                                                              |                                                                                                                                   |                            |                        |  |

|   |                                                                                                                                                                              |                                                                                                                                   |                            |                        |  |

|   |                                                                                                                                                                              |                                                                                                                                   |                            |                        |  |

| t | <ul><li>Schedule the flowgraph. registers).</li></ul>                                                                                                                        | Do not worry abo                                                                                                                  | out amount of resources (1 | for example, number of |  |

Sam Russ 3 Be Careful...Good Luck!

c. Draw a datapath that implements the flowgraph and schedule.

d. (BONUS) Create a table that shows the value of each datapath control signal on each clock cycle.

Sam Russ 4