## Programmable System-on-a-Chip (PSoC)

- CPU core + programmable logic

- PSoCs becoming more important because NRE (nonrecoverable engineering) costs keep rising as we go deeper into sub-micron and nanometer technologies

- NRE cost is the cost of the first chip

- A mask set is used to pattern layers/materials (metal, polysilicon, diffusion, etc) on wafer

- Masks are becoming increasingly expensive

- The higher the NRE, the more chips you have to sell to recover costs

- A programmable chip can be used in more applications, so more potential customers!!!

BR 1/99

| Protocol         | Channels<br>(Lanes) | I/O Baud Rate<br>(Gb/s) | Reference Clock<br>Rate (MHz) |

|------------------|---------------------|-------------------------|-------------------------------|

|                  |                     | 1.06                    | 53                            |

| Fibre Channel    | 1                   | 2.12                    | 106                           |

|                  |                     | 3.1875(1)               | 159.375                       |

| Gigabit Ethernet | 1                   | 1.25                    | 62.5                          |

| 10Gbit Ethernet  | 4                   | 3.125                   | 156.25                        |

| Infiniband       | 1, 4, 12            | 2.5                     | 125                           |

| Aurora           | 1, 2, 3, 4,         | 0.840 - 3.125           | 42.00 - 156.25                |

| Custom Protocol  | 1, 2, 3, 4,         | up to 3.125             | up to 156.25                  |

# Coding for Serial Data Transmission

- · Want to distinguish start/end of packets

- Want a certain number of signal transitions per unit time (transition density) so that receiver clock can remain synchronized to bit stream

- Want to be able to detect transmission errors.

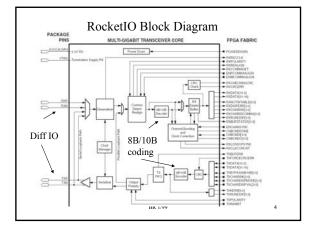

8B/10B Coding

- 8B/10B coding means that 10 bits are used to encode 256 (8-bit) data characters.

- 10 bits give 1024 combinations, why the extra bits?

- Data sent in packets that is formatted as header (start of packet), packet data, end of packet

- Need special control characters (K-characters) that will be used for start/end of packet designation, sync character, other control

- Extra bits used to encode K-characters (12 in 8B/10B code)

- Data is called D-characters

- A subset (called commas) of the K-characters has bit encoding which is guaranteed to NEVER appear in the serialized stream of D-characters.

BR 1/99

6

BR 1/99

## 8B/10B Coding (cont)

- Code is run length limited (RLL) guarantees no more than five consecutive '1's or five consecutive '0's

- Guaranteed transition density (transitions per unit time).

- Allows receiver clock PLL to remain synchronized to input data stream

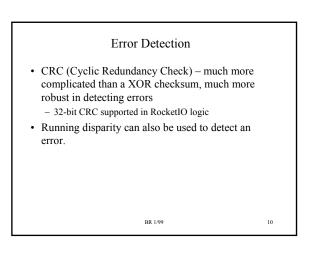

- *Disparity* difference in number of received '1's and '0's in a serial stream over some length.

- +1 disparity (one more '1' than '0')

- -1 disparity (one more '0' than '1')

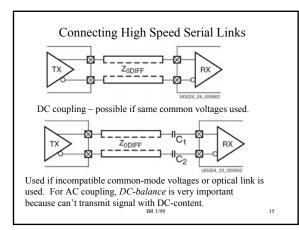

- Code is *DC-balanced* if equal numbers of '1's and '0's is sent.

BR 1/99

7

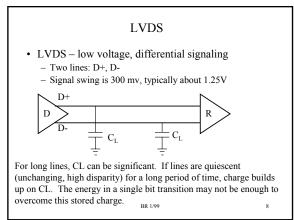

### Disparity/DC-balance, and LVDS

- If a code has low disparity (low difference in number of '0's, '1's sent) then charge does not get chance to build up.

- For a given period of time, if equal numbers of '1's, '0's is sent, this is 0 disparity. This transmission is said to be 'DC-balanced'.

- Each 10-bit symbols in the 8B/10B code either has a disparity of 0, +2 (six ones, four zeros), or -2 (four ones, six zeros)

- *Running Disparity* is the disparity for a given sequence of symbols, e.g. a packet

- Disparity for a in a 10G ethernet packet is guaranteed to be either +1 or -1.

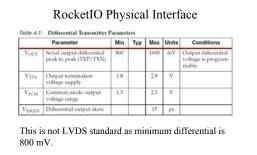

Note large common-mode range.

#### BR 1/99

11

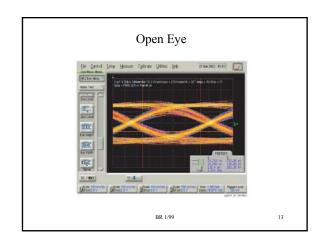

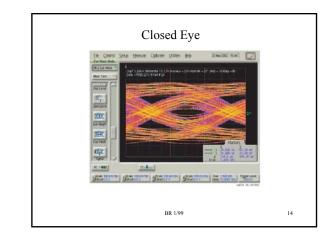

# Eye Diagram An EYE diagram used to measure quality of transmission channel. Generate pusedo-random data over channel, feed received data into vertical channel of scope Feed data rate (received generated clock) into horizontal sweep. An 'open' eye corresponds to minimal distortion. A closed eye shows signal *jitter*. *Jitter* is short term variations of a signal from its ideal position in time. Jitter caused by intersymbol interence, power supply noise, transmission channel loss. etc.

BR 1/99

12

# Virtext-II FPGA Resources

- 18x18 2's-complement multiplier

- 18Kb Dual Port SRAM blocks that can configured as shown below

| 16K x 1 bit | 2K x 9 bits   |

|-------------|---------------|

| 8K x 2 bits | 1K x 18 bits  |

| 4K x 4 bits | 512 x 36 bits |

|             |               |

|             |               |

|             |               |

|             |               |

BR 1/99

20

| CPU                                                                                                                                                     |      |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|

| • 8-bit CPU, close to a 6502 core (same core used in the Apple II and original Nintendo )                                                               |      |  |  |  |

| 8-bit Accumulator (A), 8-bit Index Register (X), 16-bit<br>Program counter, 8-bit flag register, 8-bit stack pointer<br>register                        |      |  |  |  |

| <ul> <li>6502 also had another index register (Y) that is missing in this c</li> <li>Two register banks of 256 locations each</li> </ul>                | ore. |  |  |  |

| <ul> <li>Used for RAM, also for control registers of onboard peripherals</li> <li>Non-pipelined core, all operations take at least 5 clocks,</li> </ul> |      |  |  |  |

| most 6 or 7 clocks, some take up to 13 clocks                                                                                                           |      |  |  |  |

| BR 1/99                                                                                                                                                 | 24   |  |  |  |

|                                                                                                                                                         |      |  |  |  |

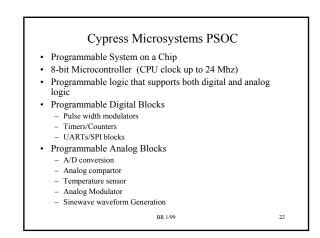

# Programmable System-on-a-Chip

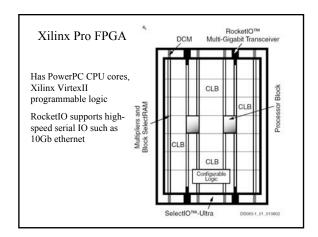

- The Xilinx-II Pro and Cypress PSOC are two examples are programmable system-on-a-chip

- Processor core + programmable Logic is a powerful combination.

- Xilinx device intended for high-end, highperformance applications

- Cypress device for low-end, low-cost.

BR 1/99

25