# Digital System Design

- At this point, we are trying to do complex datapaths + complex control

- Faced with problems of :

- Constraints minimum clock frequency, maximum number of clock cycles, target device, resource limits (don't have an infinite number of logic cells available)

- Execution unit architecture and number : fast adder? Slow adder? Pipelined or non-pipelined multiplier? SRAM versus registers? How many do I need based on constraints?

- Scheduling : what happens during what clock cycle?

BR 1/99

# Constraints Two *Constraints* that can be placed on a digital system design are clock period and clock cycle constraints A Clock period constraint will define the minimum clock frequency. Will affect the architecture of your execution units (fast adder versus slow adder, ninelined execution unit versus

- adder versus slow adder, pipelined execution unit versus non-pipelined execution unit)

- A clock cycle constraint limits the available number of clock cycles to perform operation

- Total computation time: clock period \* clock cycles

- Other constraints: Power, device type, Input/Output

### BR 1/99

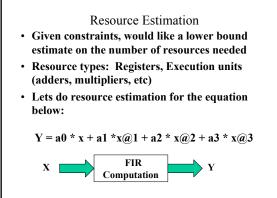

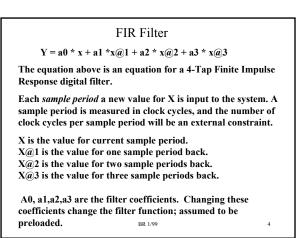

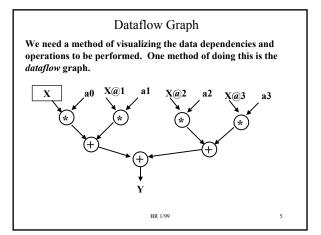

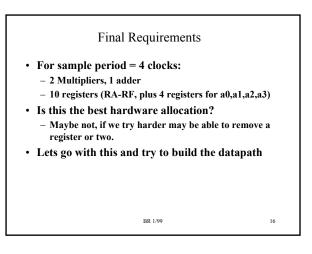

## Resource Estimation

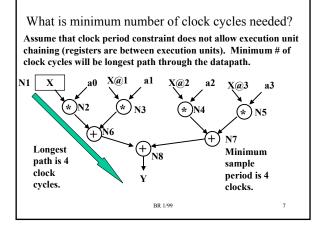

Given a clock cycle constraint (sample period), can estimate minimum number of needed resources.

Assume the minimum sample period of 4 clocks.

Minimum resource estimation is:

# operations/ # of clocks

Minimum Resource estimation: # multipliers = # multiplies/ # clocks = 4/4 = 1

# adders = # additions/ #clocks = 3 /4 = 1

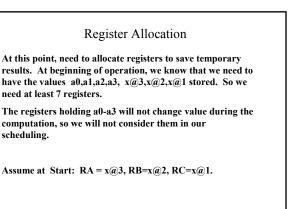

Minimum resource estimation is 1 multiplier, 1 adder. Register estimation is tougher. Need to store X@1, X@2, X@3 + four coefficents. Need at least 7 registers.  $\mathbb{R}_{\mathbb{R}^{1/99}}$

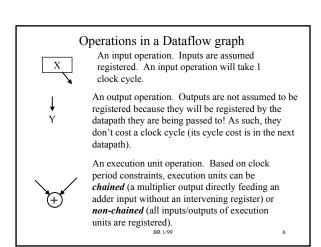

### Scheduling

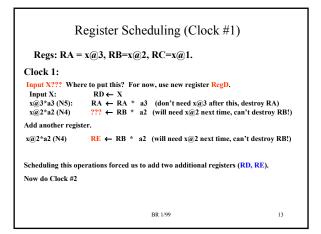

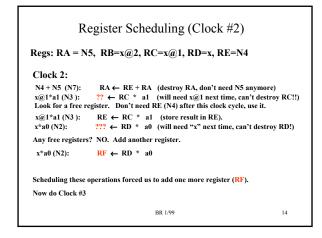

*Scheduling* is mapping operations onto execution units. Use a scheduling table which lists clock cycles versus resources. Lets first just worry about execution units, and not about registers for now.

| Resource:      | Adder         | Multiplier                 | 10      |

|----------------|---------------|----------------------------|---------|

| Cycle<br>Start |               |                            |         |

| #1             | idle          | Reg??←x@3*a3 (N5)          | Input X |

| #2             | idle          | Reg??←x@2*a2 (N4)          |         |

| #3             | N7 op (N5+N4) | Reg?? ←x@1*a1 (N3)         |         |

| #4             | idle<br>B     | Reg?? ←x*a0 (N2)<br>R 1/99 | 9       |

Scheduling Failed! The scheduling failed! We were not able to schedule the adder operations represented by nodes N6 and N8. The minimum resource estimation is a *lower bound*; may not find a schedule to fit it. If scheduling fails, the two options: a. Increase resources, keep same # of clocks b. Increase # of clocks, keep same number of resources We want a minimum sample period, so do option #a. The bottleneck is the multiplier. Lets add another multiplier.

|                            | Sche           | duling (2nd | l try)      |         |

|----------------------------|----------------|-------------|-------------|---------|

| Resource<br>Cycle<br>Start | : Adder        | Mult A      | Mult B      | ю       |

| #1                         | idle           | x@3*a3 (N5) | x@2*a2 (N4) | Input X |

| #2                         | N7 op (N5+N4)  | x@1*a1 (N3) | x*a0 (N2)   |         |

| #3                         | N6 op (N3+N2)  | idle        | idle        |         |

| #4                         | N8 op (N7+N6)  | idle        | idle        |         |

| Schedu                     | ling succeeds. |             |             | 1       |

|                            |                | BR 1/99     |             | 11      |

BR 1/99

8

Register Scheduling (Clock #3, Clock #4) Regs: RA = N7, RB=x@2, RC=x@1, RD=x, RE=N3, RF=N2 Clock 3: N6 op (N3+N2) RE ← RE + RF (destroy RE, don't need N3 anymore) Regs: RA = N7, RB=x@2, RC=x@1, RD=x, RE=N6, RF=N2 Clock 4: N8 op (N7+N6) Yout ← RA + RE (output is unregistered) What about initial conditions for next sample period? RA = x@3, RB=x@2, RC=x@1 ??  $RC \leftarrow RD$  $RB \leftarrow RC$  $x(a) 1 \leftarrow x$ Note that X in this sample period becomes X@1  $x@2 \leftarrow x@1$ for the next sample period, x@1 becomes x@2,  $x@3 \leftarrow x@2$ RA ← RB etc... BR 1/99 15

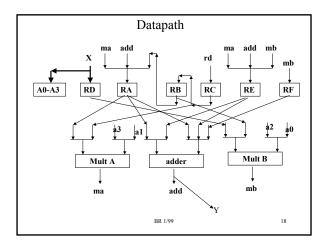

| Datapath Execution Unit                                                                                                                                       | t sources, destinations                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Mult A: Left sources: RA, RC<br>Mult B: Left sources: RB, RD<br>Adder: Left sources: RE, RA<br>RE                                                             | Right sources: a3, a1<br>Right sources: a2, a0<br>Right sources: RA, RF, |

| RA src: MultA, Adder, RB<br>RB src: RC<br>RC src: RD<br>RD src: X<br>RE src: Adder, Mult A, Mult<br>RF src: Multiplier B<br>a0-a3 registers loaded from exter |                                                                          |

| BR 1                                                                                                                                                          | 99 17                                                                    |

# Comments

- Saving on Execution units leads to lots of wiring and muxes because of the amount of execution unit sharing that is required

- Could probably have reduced some of the mux requirements by more careful assignment of temporary values to registers

- This datapath would require a FSM with four states; each state corresponding to a clock cycle.

- Output of FSM would be mux select lines, register load lines

- May need extra states if handshaking control (input\_rdy, output\_rdy) is required.

BR 1/99

19

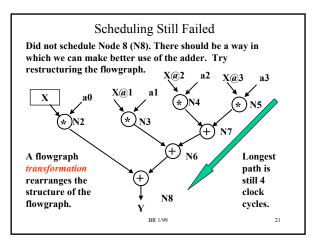

| rid of mu      | ltiplier.       |                    | -     |

|----------------|-----------------|--------------------|-------|

| Resource:      | Adder           | Multiplier         | 10    |

| Cycle<br>Start |                 |                    |       |

| #1             | idle            | Reg??←x@3*a3 (N5)  | Input |

| #2             | idle            | Reg??←x@2*a2 (N4)  |       |

| #3             | N7 op (N5+N4)   | Reg?? ←x@1*a1 (N3) |       |

| #4             | idle            | Reg?? ←x*a0 (N2)   |       |

| #5             | N6 op (N2 + N3) | idle               |       |

|                | Try again with S     | Sample Period = 5  |         |

|----------------|----------------------|--------------------|---------|

| Resource:      | Adder                | Multiplier         | 10      |

| Cycle<br>Start |                      |                    |         |

| #1             | idle                 | Reg??←x@3*a3 (N5)  | Input X |

| #2             | idle                 | Reg??←x@2*a2 (N4)  |         |

| #3             | N7 op (N5+N4)        | Reg?? ←x@1*a1 (N3) |         |

| #4             | N6 op (N3+N7)        | Reg?? ←x*a0 (N2)   |         |

| #5             | N8 op (N2 + N6)      | idle               |         |

| Schedulir      | ng succeeds with new | flowgraph!!!!!     | 1       |

|                | F                    | BR 1/99            | 22      |

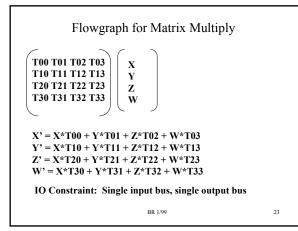

BR 1/99

25

| Input X0<br>Input Y0 (compute) |             | it Rate=4            | Note t         | hat for this over   | lap |

|--------------------------------|-------------|----------------------|----------------|---------------------|-----|

| Input Z0 (compute)             |             |                      | case t         | he input bus is     | •   |

| Input W0 (compute)             | *           |                      |                | antly busy, and the | 10  |

| compute                        | Input X1    |                      |                | 5 57                |     |

| compute                        | Input Y1 (c |                      | outpu          | t bus is constantl  | y   |

| compute                        | Input Z1(co |                      | busy.          |                     |     |

| compute                        | Input W1 (c |                      | 2              |                     |     |

| Output X0'                     | compute     | Input X2             | <del>.</del> . |                     |     |

| Output Y0'                     | compute     | Input Y2             |                |                     |     |

| Output W0'<br>Output Z0'       | compute     | Input Z2             |                |                     |     |

| Output Z0                      | compute     | Input W2             | (compute       |                     |     |

| atency=12                      | Output X1'  |                      |                | Input X3            |     |

| atericy=12                     | Output Y1'  |                      |                | Input Y3 (compute)  |     |

|                                | Output W1   |                      |                | Input Z3(compute)   |     |

|                                | Output Z1'  | compute<br>Output X  | <b>2</b> ,     | Input W3 (compute)  |     |

|                                |             | Output X<br>Output Y |                | <u>co</u> mpute     |     |

|                                |             | Output Y             |                | <u>co</u> mpute     |     |

|                                |             | Output W             |                | compute             |     |

|                                |             | Output Z.            | <u>-</u>       | compute             |     |

|                                |             | BR 1/99              |                | etc                 | 30  |