## Comments about ASM Example

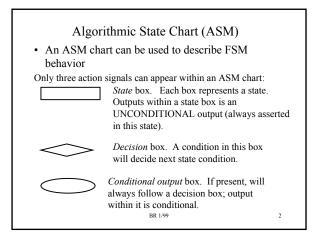

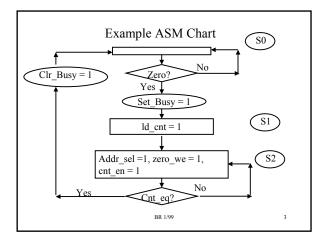

- · How many states?

- Three states, count the boxes

- · How many inputs?

- Two inputs (Zero, Cnt\_eq). Count signals within decision boxes. Inputs ALWAYS appear within decision boxes.

- · How many outputs?

- 4 unconditional outputs (count signals within state boxes)

- 2 conditional output (count signals within conditional output boxes

- Outputs ALWAYS appear in either state boxes or conditional output boxes.

BR 1/99

CLK

### State Encoding

- How we encode the states is an implementation decision

- For K states, need a minimum of log<sub>2</sub>(K) Dffs.

- · Minimal encoding for example is two FFs

- S0 = 00, S1 = 01, S2 = 10 (counting order)

- S0 = 00, S1 = 01, S2 = 11, (Gray code for S0->S1->S2) Gray code usually faster, less logic than counting order

- · One Hot encoding, one FF per state

- S0 = 001, S1 = 010, S2 = 100

- For large FSMs (> 16 states), one hot can be faster than minimal encoding

BR 1/99

7

# FSM Entity Declaration, Part of Architecture library iece; use iece.std\_logic\_1164.all; --FSM entity for RAM Zero example entity ramfsm is port ( elk, reset: in std\_logic; -- control inputs set\_busy, ct\_busy: out std\_logic; -- control outputs addr\_sel, cnt\_en, ld\_ent, zero\_we: out std\_logic; state: out std\_logic\_vector(1 downto 0)) -- state out for debugging ); end ramfsm; architecture a of ramfsm is signal pstate: std\_logic\_vector(1 downto 0);="00"; --- state encoding CONSTANT S0: std\_logic\_vector(1 downto 0):="00"; CONSTANT S1: std\_logic\_vector(1 downto 0):="01"; CONSTANT S2: std\_logic\_vector(1 downto 0):="10";

### FSM Architecture, One process (cont)

|   | begin                 |                                                     |

|---|-----------------------|-----------------------------------------------------|

|   | state <= pstate;      | look at present state for debugging purposes        |

|   | stateff:process(clk)  | process has state transitions ONLY                  |

|   | begin                 |                                                     |

|   | if (reset = '1') then | pstate <= S0;                                       |

|   | elsif (clk'event and  | clk='1') then rising edge of clock                  |

|   | CASE pstate           | e IS                                                |

|   | WHEN SO               | ) => if (zero = '1') then pstate <= S1; end if;     |

|   | WHEN S1               | => pstate <= S2;                                    |

|   | WHEN S                | S2 => if (cnt_eq = '1') then pstate <= S0 ; end if; |

|   | WHEN c                | others => pstate <= S0;                             |

|   | end case;             |                                                     |

|   | end if;               |                                                     |

|   | end process stateff;  |                                                     |

|   |                       |                                                     |

|   | set_busy <= '1' when  | (pstate = S0 and zero = '1') else '0';              |

|   | ld_cnt <= '1' when (p | state = S1) else '0';                               |

|   | addr_sel <= '1' when  | (pstate = S2) else '0';                             |

|   | zero_we <= '1' when   | (pstate = S2) else '0';                             |

|   | cnt_en <= '1' when (p | ostate = S2) else '0';                              |

|   | clr_busy <= '1' when  | $(pstate = S2 and cnt_{eq} = '1') else '0';$        |

| 4 | end a;                | BK 1/99                                             |

|   |                       |                                                     |

### Comments on One Process Implementation

- *Stateff* process defines state FFs and transistions between states

- Outputs of FSM are separate concurrent statements outside of process

- Can be confusing since you separate out the FSM outputs from their state definitions within the CASE statement

- If output code is placed within CASE statement then they would be protected by the clock check and thus would have DFFs placed on their outputs

1 clock cycle of latency to output assertion

BR 1/99

10

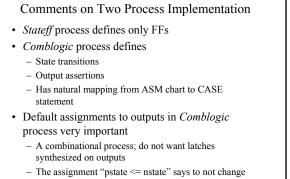

### FSM Architecture, Two processes architecture a of ramfsm is signal pstate, nstate: std\_logic\_vector(1 downto 0); CONSTANT S0 : std\_logic\_vector(1 downto 0) := "00"; --- state encoding CONSTANT S1 : std\_logic\_vector(1 downto 0) := "01"; CONSTANT S2 : std\_logic\_vector(1 downto 0) := "10"; begin state <= pstate; -- look at present state for debugging purposes stateff:process(clk) -- process has DFFs only begin if (reset = '1') then pstate <= S0; elsif (clk'event and clk='1') then pstate <= nstate; -- updated present state with next state endif end process stateff: BR 1/99 11

| FSM Architecture, Two processes (cont)                                            |    |

|-----------------------------------------------------------------------------------|----|

| comblogic: process (zero, cnt eq, pstate)                                         |    |

| begin                                                                             |    |

| default assignments                                                               |    |

| nstate <= pstate;                                                                 |    |

| set busy $\leq 0'$ ; clr busy $\leq 0'$ ;                                         |    |

| $ld cnt \leq 0';$                                                                 |    |

| addr sel <= '0';                                                                  |    |

| $zero we \le '0';$                                                                |    |

| $en \le 0;$                                                                       |    |

| CASE pstate IS                                                                    |    |

| $\dot{W}$ HEN S0 => if (zero = '1') then                                          |    |

| set busy <= '1'; nstate <= S1;                                                    |    |

| end if;                                                                           |    |

| WHEN S1 => ld cnt <= '1'; nstate <= S2;                                           |    |

| WHEN S2 $\Rightarrow$ zero we $\leq$ '1'; cnt en $\leq$ '1'; addr sel $\leq$ '1'; |    |

| if (cnt $eq = '1'$ ) then                                                         |    |

| clr busy <= '1'; nstate <= S0 ;                                                   |    |

| end if;                                                                           |    |

| WHEN others => nstate <= S0;                                                      |    |

| end case;                                                                         |    |

| end if;                                                                           |    |

| end process comblogic; BR 1/99                                                    | 12 |

| end a;                                                                            |    |

state unless directed to from within CASE statement.

BR 1/99

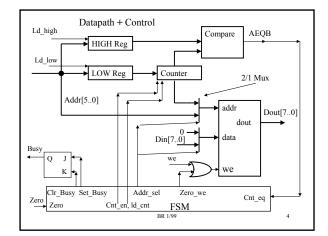

### Comments

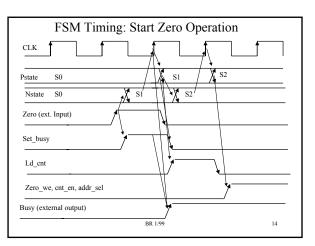

- Note that Pstate changes on active clock edge

- Conditional outputs will change based on present state AND external inputs

- Unconditional outputs change on clock edge and remain true as long as in the current state

- In order for BUSY to go high in State S1, 'set\_busy' must be asserted in S0 since BUSY comes from JK FF.

BR 1/99

15

13

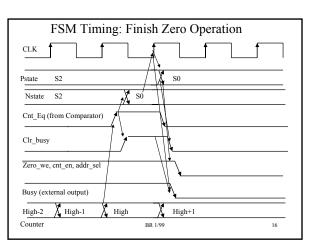

# Comments

- Note that for BUSY to go low in S0, then "clr\_busy" had to be asserted in State S2.

- Note that the 'cnt\_en' signal stays true for one clock edge after 'cnt\_eq' goes true

- This means that the COUNTER will increment to HIGH+1, sometimes this makes a difference, need to be aware of it

```

BR 1/99

```

17