#### DataPath Elements

- Altera LPM library has many elements useful for building common datapath functions

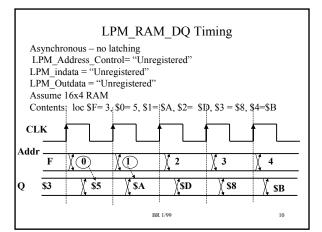

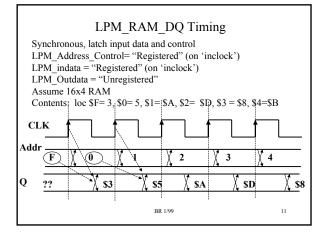

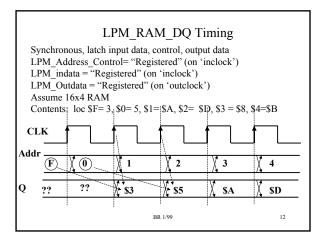

- lpm\_ram\_dq recommended for either asynchronous or synchronous RAM. Uses EAB in Flex 10K family.

- lpm\_ram\_io recommended for asynchronous RAM. Uses EAB in Flex 10K in family.

- lpm\_compare comparing two values. Outputs are AEQB, ALB, ALEB, AGB, AGEB

- lpm\_counter versatile counter function

BR 1/99

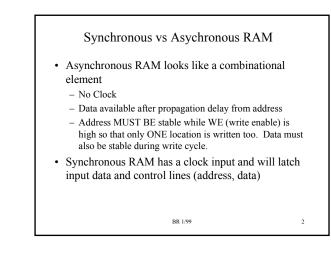

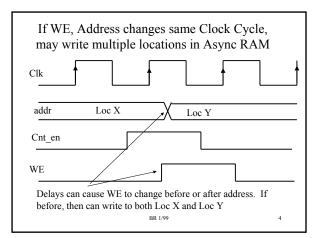

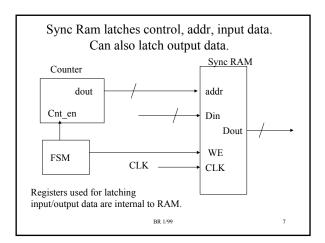

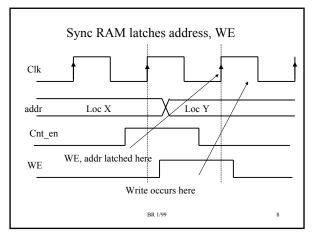

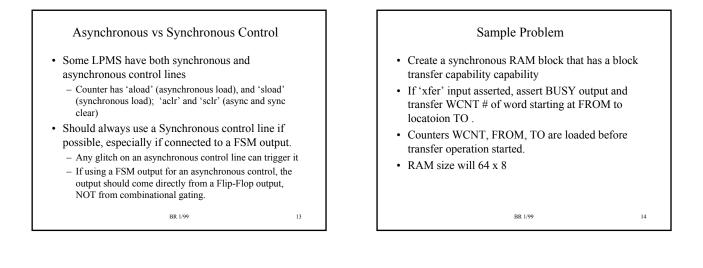

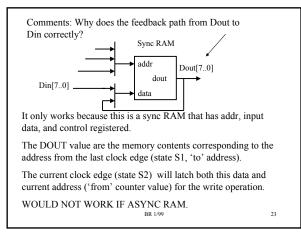

#### Will usually prefer Sync Ram

- Sync RAM is easier to use from a timing perspective but adds latency to operations

- If address coming from counter, then have an extra clock cycle of latency from when counter value is updated to when RAM data is available for that address

- In our Lab exercises and class examples, will normally use synchronous RAM

- Will not latch output data unless specifically needed

- Options to latch control, input data, output data available on LPM\_RAM\_DQ

#### BR 1/99

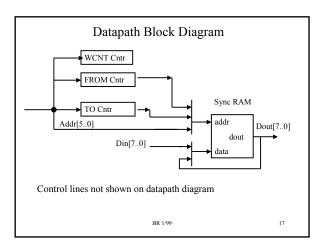

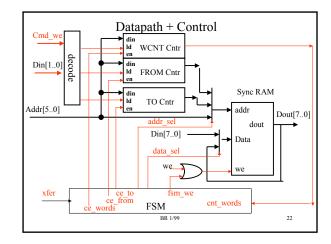

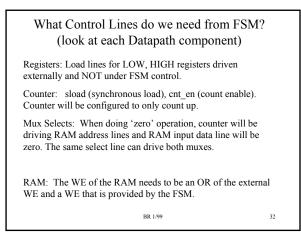

# What Control Lines do we need from FSM? (look at each Datapath component)

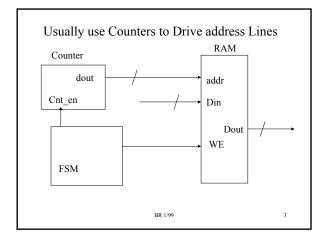

Counters: Load lines for WCNT, TO, FROM registers driven externally and not under FSM control. Count enables for these counters need to be exercised by FSM. WCTN will be configured to count DOWN, the TO,FROM counters will count UP.

Mux Selects: When doing 'xfer' operation, counters will be driving RAM address lines and RAM input data line will be a feedback from the RAM output.

RAM: The WE of the RAM needs to be an OR of the external WE and a WE that is provided by the FSM.

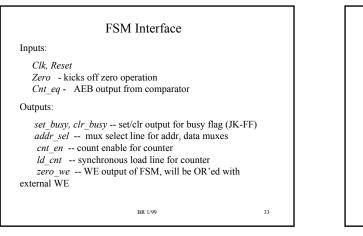

## FSM Interface

Inputs:

- Clk, Reset

- *xfer* kicks off transfer operation

*cnt\_words[5..0]* - WCNT counter value – need to check this to see if finished.

#### Outputs:

- busy busy output

- *addr\_sel[1..0]* -- mux select line for addr muxes

• *ce\_from, ce\_to, ce\_words* -- count enables for FROM, TO, WCNT counters

19

- fsm\_we -- WE to RAM

- data\_sel mux select line for RAM input data mux

BR 1/99

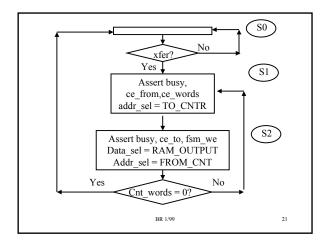

What operations do we need for FSM?

Wait for XFER command (FSM simply waits for *'xfer'* input to be asserted).

Read a value from RAM using TO counter address; increment the TO counter and decrement the WCNT counter

Write data value to RAM via FROM address counter; increment the FROM counter. Loop to read state unless WCNT counter value = 0.

FSM. Cannot do both a Read and Write in the same

20

clock cycle.

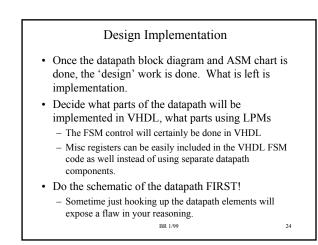

#### Design Implementation (cont.)

- After Datapath is finished, do FSM VHDL code

- ALWAYS bring the FSM state value out as an external output for debugging purposes!!!

- Should be able to write FSM code directly from ASM chart

- DEBUG take a systematic approach

- Your design will NOT WORK the first time be prepared to debug.

- Attach external pins to as many internal nets as possible so that you can observe the internal net values

- Debug your design ONE state at a time. Do not test the next state until the current state works as expected.

BR 1/99

25

27

### Design Implementation (cont.)

- Until you get more confident with VHDL, should use as many LPM components as you can

- Can easily examine input/outputs to LPMs in waveform viewer so makes it easier to debug

- · Always use a VERY LONG clock cycle to start out with so that you do not encounter timing problems

- To be absolutely safe, make external inputs change on the falling edge if your internal logic is rising edge triggered (this gives you 1/2 clock of setup time).

BR 1/99

26

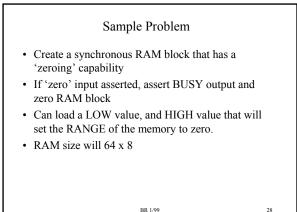

The remaining slides are from an older discussion about a RAM with zeroing capability.

The implementation is similar to that of the RAM with block transfer capability.

The Zero'ing RAM shows an alternate method for implementing the busy flag.

A separate register is used to hold the LOW value instead of simply using the counter for this storage. The only advantage to this is that the LOW value is preserved after a zero operation and could be reused.

BR 1/99

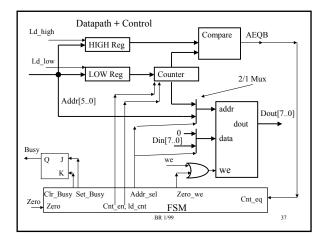

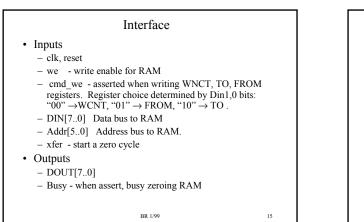

Interface

# - low ld - load LOW value; will be taken from address

- low high load HIGH value; will be taken from address bus

- DIN[7..0] Data bus to RAM

- Addr[5..0] Address bus to RAM.

- Zero start a zero cycle

- Outputs

Inputs

- clk, reset

bus

- DOUT[7..0]

- Busy when assert, busy zeroing RAM

BR 1/99

29

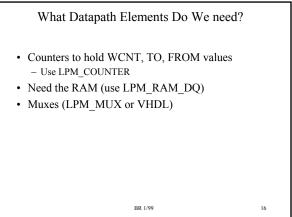

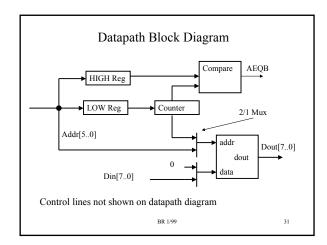

#### What Datapath Elements Do We need?

- · Two registers to hold LOW, HIGH value - Use LPM DFF or write VHDL model (reg6.vhd)

- Need a 6-bit counter to cycle address lines of RAM - LPM COUNTER

- Counter needs to be loaded with LOW value when we start to zero the RAM

- · Need a Comparator to compare Counter value and HIGH value to see if we are finished

- Need the RAM (use LPM RAM DQ)

- Muxes (LPM MUX or VHDL)

BR 1/99

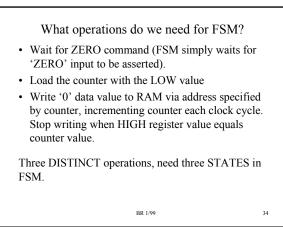

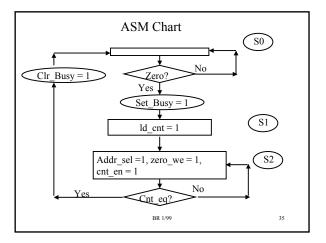

#### ASM States

- Three States

- State S0 waits for Zero operation. In this state the external addr, data, we lines are muxed to RAM. Set busy flag on transition to State S0.

- State S1 loads counter with LOW register value

- State S2 does zero operation. Exit this state with counter value equals to HIGH register value. On state exit, clear the busy flag output (conditional output).

- We will spend HIGH-LOW+1 clocks in this state (clear LOW to HIGH locations inclusive)