#### The Concept of a Fault

- Testing centers around detection of *faults* in a circuit.

- The digital world is made up of interconnected gates

- Thus, only two things can fail gates and their interconnections

- A faulty gate fails to perform its function correctly

- A faulty interconnection produces a "stuck at 1", "stuck at 0", or permanently tri-stated input.

- Problem: can you set up experiments that produce one result if the gate/interconnect is good, and another if it is bad?

- · This leads to two closely related concepts.

ed from Prof Sam Russ

BR 1/99

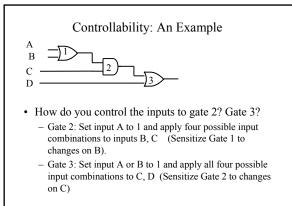

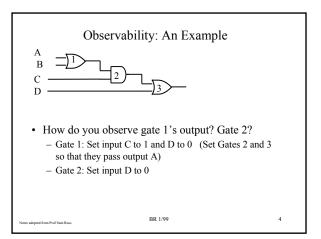

## Observability and Controllability

- Observability is the ability to observe a gate output directly at external pins

- Controllability is the ability to apply any and all desired inputs to a gate via external pins

- Test a gate completely, all combinations of inputs must be applied and the output corresponding to each input must be observed

BR 1/99

2

BR 1/99

3

## Extending the Concept

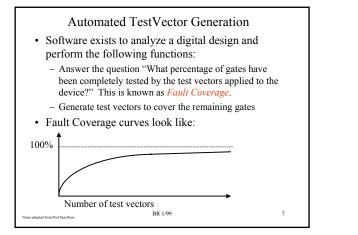

- A set of inputs and outputs designed to test a specific gate is called a *test vector*.

- A collection of inputs designed to test a specific gate or area completely is called a *test vector suite*.

- Once a test vector suite is developed for a block, you need to develop a way to get those inputs to the block and directly observer the block's outputs

#### BR 1/99

Some Problems

- #1: Four additional test vectors are required for every additional 2-input gate. The number of test vectors increases as the number of gates increases.

- #2: The number of gates is increasing much faster than the number of inputs/outputs. This is making both controllability and observability more difficult.

- #3: Sequential circuits can be notoriously difficult to test. For example, a 16-bit counter has to cycled through its entire count for complete testing.

- Some strategies have emerged to deal with these problems.

BR 1/99

,

## Built-In Self Test (BIST)

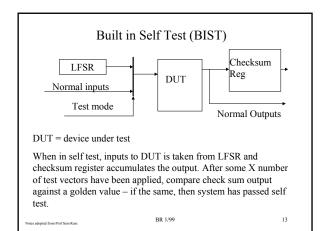

- One way to add reliablity to a component or part of a chip is with Built-In Self Test (BIST)

- An example is the Motorola 68030 MCU

- Motorola has added a small set of instructions which they certify tests a significant fraction of the 68030's gates.

- Can be incorporated into the low level startup process to detect and processor faults.

BR 1/99

# **BIST Approach**

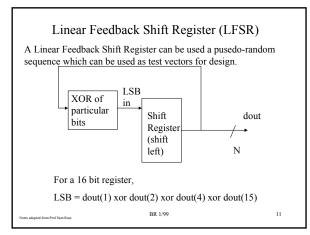

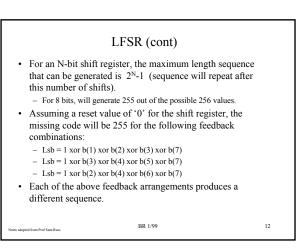

- Add circuitry so that on powerup a small ROM or pseudo-random sequence generator applies a series of inputs

- The outputs are tested for a correct answer, usually by accumulating the outputs into a checksum value (either by XOR or Cyclic Redundancy Check -CRC)

- · The psuedo random pattern generation and checksum accumulation does not need many gates

- · The probability of passing self-test with an undiagnosed fault can be made small (depends on number of patterns). BR 1/99

10

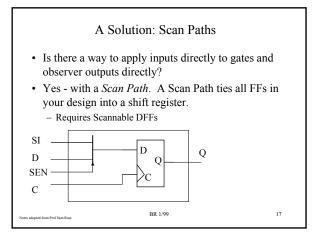

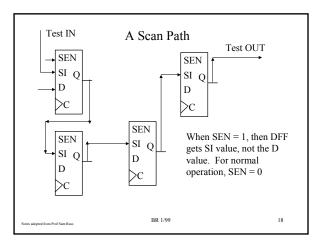

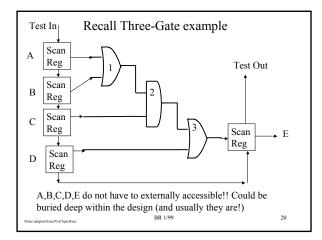

#### Scan Path Operation

- Assume ALL FFs in design are in tied into a Scan Path and let there be N FFs.

- Apply SEN = '1', and clock test vector serially into scan path. Will take N clocks.

- Apply, SEN = '0', and clock ONCE. This will test the design using the test vector!

- Apply SEN = '1', and clock in next test vector. At same time, you clocking OUT the result of the last test vector!!!

- After first test vector, each test vector takes N+1 clocks!!

BR 1/99

ated from Prof Sam Russ

of from Prof Sam Pure

19

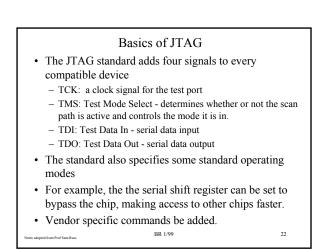

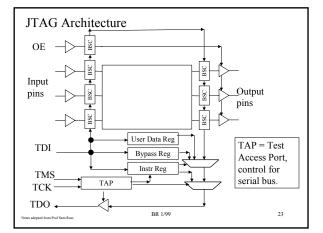

#### Introducing IEEE 1149.1 (JTAG)

- In order to standardize scan path design and support, the Joint Test Action Group, comprised of over 200 electronics companies, developed an industry-wide standard for scan path support

- · It has been adopted as IEEE Standard 1149.1

- It is usually called "the JTAG port" in sales literature (or Boundary Scan)

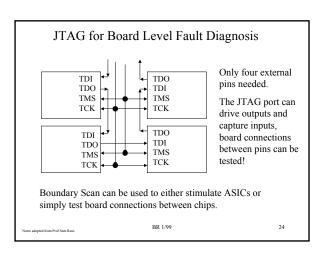

- Every JTAG compatible port can be chained together to form a serial device

- Can be used to support fault dection at the single chip level, detection of board level faults, and even some PLDs/FPGAs can be programmed with it.

## Some Keys to an Effective Test Strategy

- Decide early, not late, on test strategy – Other test approaches beside BIST, JTAG

- Identify software tools for test vector generation, fault grading

- Have to plan test strategy through development, prototyping, manufacturing, and maintenance

- Adding a JTAG bus to a board (and JTAG compatible components) can be a cost effective way of adding a large amount of testability to your design

BR 1/99

forted from Prof Sam Russ

25

Summary

The purpose of testing is to uncover faults in a system (chip or board)

Faults are found by applying test vectors and observing results

Test vectors can be generated manually or automatically

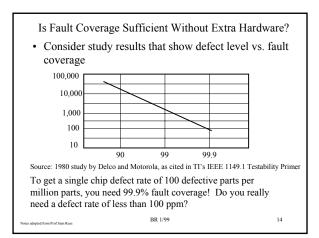

Usually have to add extra hardware to improve testability.

Scan paths can increase chip and board level testability.

JTAG adds four pins and supports a variety of test modes; almost all electronics vendors support JTAG.