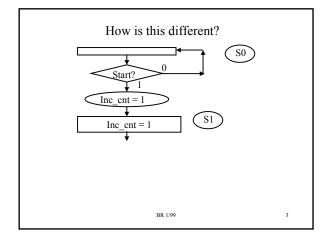

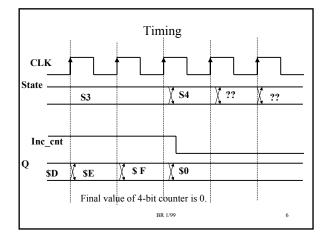

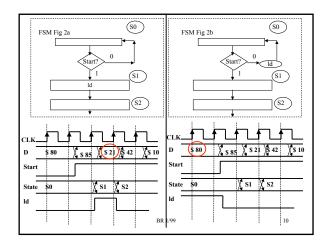

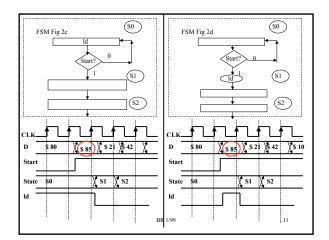

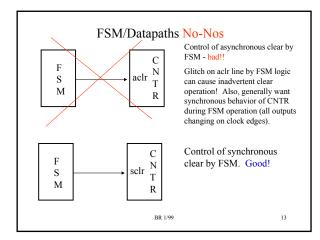

What Causes Glitches on outputs of FSMs?

- Many combinational paths in logic that defines next state.

- If these paths have unequal numbers of gates, or gates have different delays, then glitches can occur.

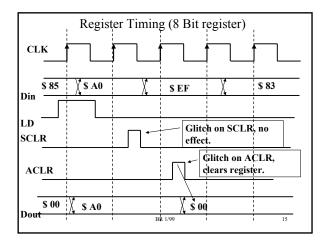

- We normally don't care about these glitches as long as the output lines are STABLE before the next clock edge (satisfy the setup time requirement)

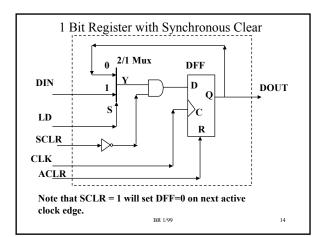

- If output lines are connected to asynchronous control inputs, then glitches can be a BIG problem!

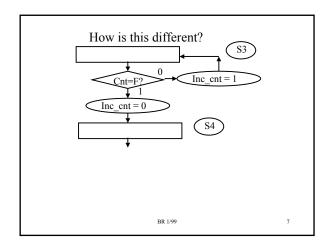

- Solution: Don't connect asynchronous controls lines to FSM outputs or guarantee FSM outputs are glitch free (come directly from a FF).