- We will review the arithmetic building blocks we have previously used, and look at some new ones.

- Addition

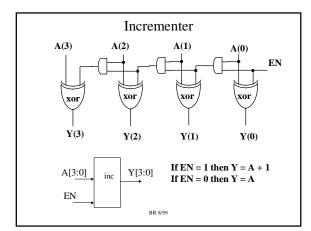

- incrementer

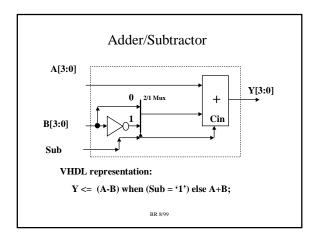

- Addition/subtraction

- decrementer

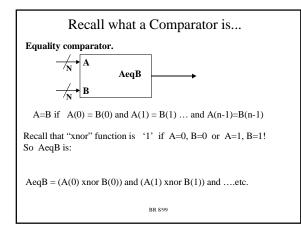

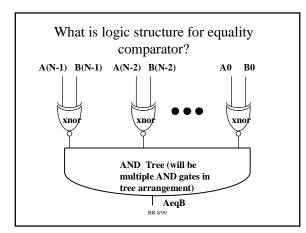

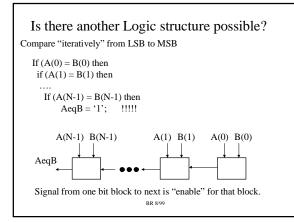

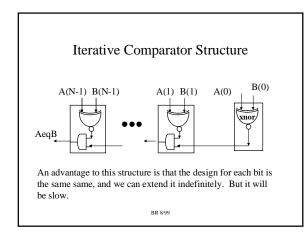

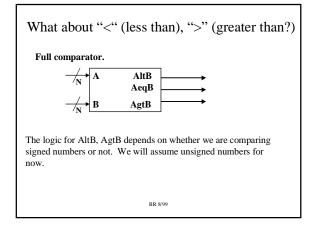

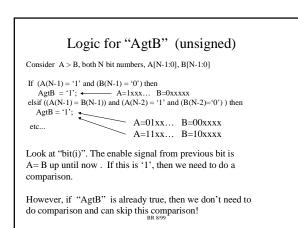

- Comparison

BR 8/99

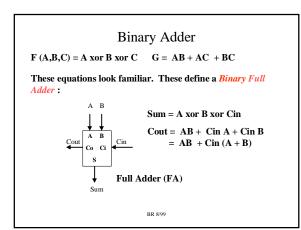

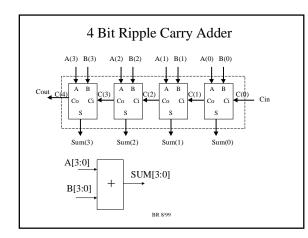

How did we get the Incrementer equations? Full Adder equations: Sum = A xor B xor Cin Cout = AB or Cin A or Cin B = AB or Cin (A or B) Let B = 0, Cin = 1 so that Sum = A + 1. Then equations simplify to: SUM = A xor 1 xor 0 = A xor 1 = A' Cout = 0 or 1 (A or 0) = A. If we want an "En" input, then we want SUM = A if En=0, else SUM = A+1 if En = '1'. Filling in the above equations: SUM = A En' or A' En = A xor En Cout = A En (note that Cout = 0 if En = 0).

The "Cout" of one bit becomes the "En" signal for the next bit!!!!

BR 8/99

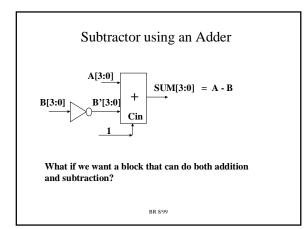

## A Subtractor

What is subtraction?

$\mathbf{A} - \mathbf{B} = \mathbf{A} + (-\mathbf{B})$

How do you take the negative of a number? Depends on the sign representation (signed magnitude, 1s complement, 2s complement). Lets assume 2's complement since it is most common).

(-B) = B' + 1So: A - B = A + (-B) = A + B' + 1

BR 8/99

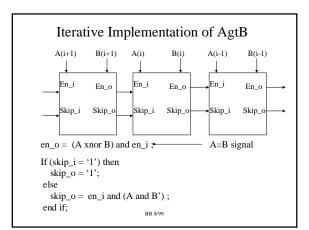

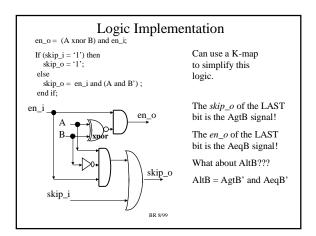

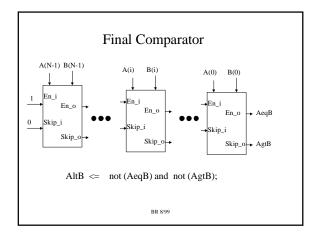

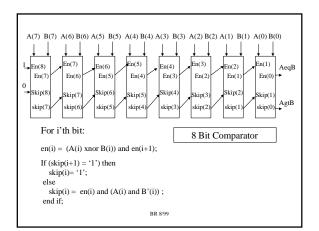

| architecture a of comp is<br>signal en, skip: std_logic_vector(8 downto 0);           |                                                                      |

|---------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| begin<br>aeqb <= en(0);<br>agtb <= skip(0);<br>altb <= (not en(0)) and (not skip(0)); | VHDL architecture that<br>implements comparator<br>logic as shown on |

| process (a,b)<br>begin<br>en(8) <= '1'; skip(8) <= '0';<br>for i in 7 downto 0 loop   | previous slides.                                                     |

| en(i) <= not (a(i) xor b(i)) and $en(i+if (skip(i+1) = 1) thenskip(i) <= 1$ ;         | 1);                                                                  |

| else<br>skip(i) <= en(i+1) and (a(i) and no<br>end if;<br>end loop;                   | ot b(i));                                                            |

| end ioop;<br>end process;<br>end a; BR 89                                             | 9                                                                    |