## Programmable Logic

- So far, have only talked about PALs (see 22V10 figure next page).

- What is the next step in the evolution of PLDs?

- More gates!

4/18/00

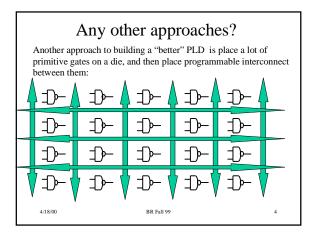

• How do we get more gates? We could put several PALs on one chip and put an interconnection matrix between them!!

BR Fall 99

– This is called a Complex PLD (CPLD).

22V10 PLD

#### Field Programmable Gate Arrays

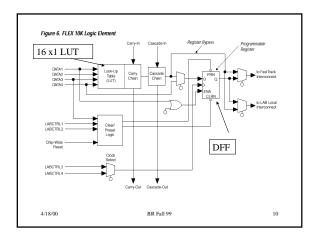

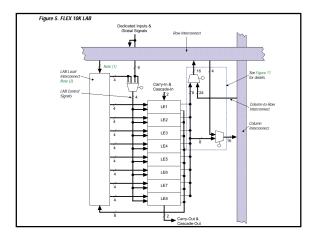

The FPGA approach to arrange primitive logic elements (logic cells) arrange in rows/columns with programmable routing between them.

What constitutes a primitive logic element? Lots of different choices can be made! Primitive element must be classified as a "complete logic family".

- A primitive gate like a NAND gate

- A 2/1 mux (this happens to be a complete logic family)

- A Lookup table (I.e, 16x1 lookup table can implement any 4 input logic function).

5

Often combine one of the above with a DFF to form the primitive logic element. 4/18/00 BR Fall 99

#### Other FPGA features

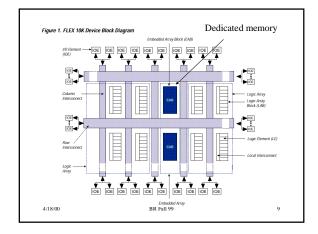

- Besides primitive logic elements and programmable routing, some FPGA families add other features

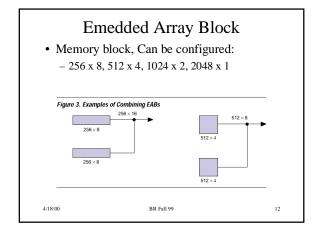

- · Embedded memory

- Many hardware applications need memory for data storage. Many FPGAs include blocks of RAM for this purpose

- Dedicated logic for carry generation, or other arithmetic functions

- Phase locked loops for clock synchronization, division, multiplication.

| Table 1. FLEX 10K Device Features          |                       |                     |                       |                     |                       |  |  |

|--------------------------------------------|-----------------------|---------------------|-----------------------|---------------------|-----------------------|--|--|

| Feature                                    | EPF10K10<br>EPF10K10A | EPF10K20            | EPF10K30<br>EPF10K30A | EPF10K40            | EPF10K50<br>EPF10K50V |  |  |

| Typical gates (logic and RAM),<br>Note (1) | 10,000                | 20,000              | 30,000                | 40,000              | 50,000                |  |  |

| Usable gates                               | 7,000 to 31,000       | 15,000 to<br>63,000 | 22,000 to 69,000      | 29,000 to<br>93,000 | 36,000 to<br>116,000  |  |  |

| Logic elements (LEs)                       | 576                   | 1,152               | 1,728                 | 2,304               | 2,880                 |  |  |

| Logic array blocks (LABs)                  | 72                    | 144                 | 216                   | 288                 | 360                   |  |  |

| Embedded array blocks (EABs)               | 3                     | 6                   | 6                     | 8                   | 10                    |  |  |

| Total RAM bits                             | 6,144                 | 12,288              | 12,288                | 16,384              | 20,480                |  |  |

| Maximum user I/O pins                      | 134                   | 189                 | 246                   | 189                 | 310                   |  |  |

| Table 2. FLEX 10K Device Features          |                   |                         |                      |                       |  |  |  |

|--------------------------------------------|-------------------|-------------------------|----------------------|-----------------------|--|--|--|

| Feature                                    | EPF10K70          | EPF10K100<br>EPF10K100A | EPF10K130V           | EPF10K250A            |  |  |  |

| Typical gates (logic and<br>RAM), Note (1) | 70,000            | 100,000                 | 130,000              | 250,000               |  |  |  |

| Usable gates                               | 46,000 to 118,000 | 62,000 to<br>158,000    | 82,000 to<br>211,000 | 149,000 to<br>310,000 |  |  |  |

| LEs                                        | 3,744             | 4,992                   | 6,656                | 12,160                |  |  |  |

| LABs                                       | 468               | 624                     | 832                  | 1,520                 |  |  |  |

| EABs                                       | 9                 | 12                      | 16                   | 20                    |  |  |  |

| Total RAM bits                             | 18,432            | 24,576                  | 32,768               | 40,960                |  |  |  |

| Maximum user I/O pins                      | 358               | 406                     | 470                  | 470                   |  |  |  |

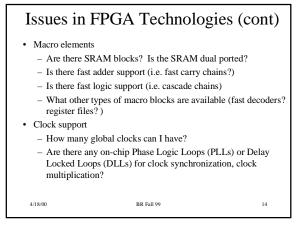

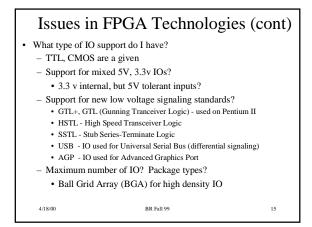

### Issues in FPGA Technologies

- · Complexity of Logic Element

- How many inputs/outputs for the logic element?

- Does the basic logic element contain a FF? What type?

- Interconnect

- How fast is it? Does it offer 'high speed' paths that cross the chip? How many of these?

- Can I have on-chip tri-state busses?

- How routable is the design? If 95% of the logic elements are used, can I route the design?

- More routing means more routability, but less room for logic elements

BR Fall 99

13

4/18/00

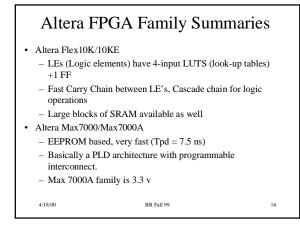

# Xilinx FPGA Family Summaries

- Virtex Family

- SRAM Based

- Largest device has 1M gates

- Configurable Logic Blocks (CLBs) have two 4-input LUTS, 2 DFFs

- Four onboard Delay Locked Loops (DLLs) for clock synchronization

- Dedicated RAM blocks (LUTs can also function as RAM).

- Fast Carry Logic

- XC4000 Family

- Previous version of Virtex

- No DLLs, No dedicated RAM blocks

- 4/18/00

- BR Fall 99

- MXDS Family

- Fine grain Logic Elements that contain Mux logic + DFF

- Embedded Dual Port SRAM

- One Time Programmable (OTP) means that no

- configuration loading on powerup, no external serial ROM – AntiFuse technology for programming (AntiFuse means

- that you program the fuse to make the connection). - Fast (Tpd = 7.5 ns)

- Fast (1pd = /.5 ns)

- Low density compared to Altera, Xilinx maximum number of gates is 36,000

BR Fall 99

18

17

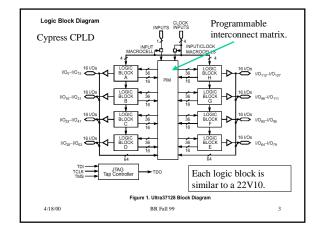

# Cypress CPLDs

- Ultra37000 Family

- 32 to 512 Macrocells

- Fast (Tpd 5 to 10ns depending on number of macrocells)

BR Fall 99

- Very good routing resources for a CPLD

4/18/00

19