# **Drive Control**

## Altera Technology Roadshow 2013

#### **Challenges for Drive Manufacturers**

#### Performance Improvements

- Higher switching frequencies, higher dynamic response

- Adapting to latest technologies

- Multi-axis, On-line Diagnostics

#### Differentiation While Lowering Costs

- Multiple Industrial Ethernet (IE) and encoder protocols

- Integrating functions into fewer components, drive miniaturization, platforms

#### Implementing Functional Safety

-Cost overhead and time to market impact

- Not always customer core competence

Challenge Across All Types of Drives Manufacturers

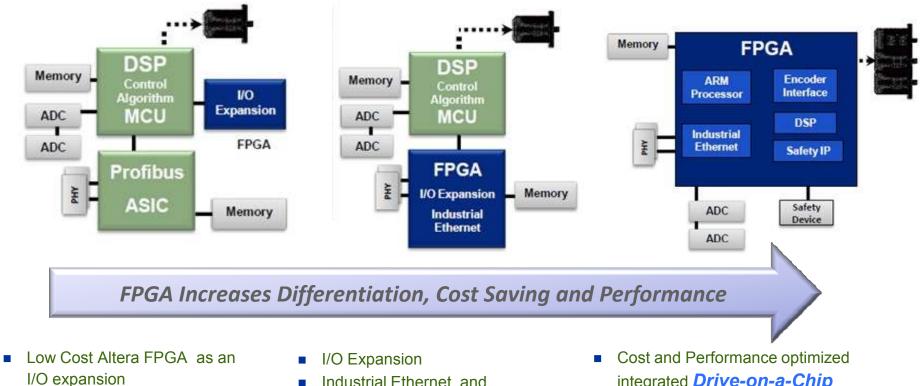

## **FPGA in Drives**

- Industrial Ethernet and Fieldbus IP

- Encoder IP

- Control Algorithm HW Acceleration

- integrated Drive-on-a-Chip

- Multi-axis control significant system cost reduction

#### As FPGA Content Increases, System Costs Decreases!

# **Drive Content Expansion with FPGA**

# **Altera Industrial Ethernet Solution**

## **Industrial Ethernet Solution 2013**

<u>All protocols</u> enabled by the same CPLD – one at a time <u>All protocols</u> have a common SW API and a common HW interface

MEASURABLE ADVANTAGE

# **Altera Industrial Ethernet Roadmap**

© 2013 Altera Corporation—Public

## <u>2013</u>

- Include EtherCAT within the same model

- One CPLD for ALL protocols

## <u>2014</u>

Optimize protocols for next generation low cost components

# **FPGA Co-Processors for CPU/MCU**

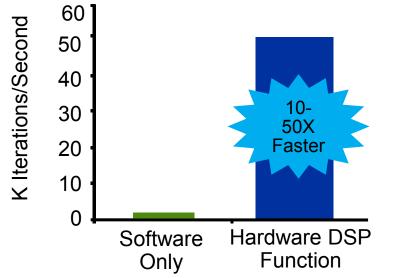

## Offload DSP algorithm from CPU

- Custom hardware block implements complete DSP datapath, <u>offloads CPU</u> to run other tasks

- Memory mapped register access between CPU & hardware

- Floating-point and variable width fixed-point arithmetic supported

| Algorithm                       | Folding | LE Usage | Multiplier<br>Usage | Algorithm<br>Latency (µs) |

|---------------------------------|---------|----------|---------------------|---------------------------|

| Floating-point single-precision | None    | 20K      | 56                  | 1.0                       |

| Floating-point single-precision | Enabled | 7.5K     | 5                   | 1.73                      |

| 16-bit fixed-point              | None    | ЗK       | 16                  | 0.22                      |

| 16-bit fixed point              | Enabled | 2K       | 1                   | 0.88                      |

MEASI DABI E ADVANTAGE

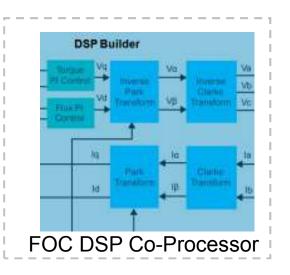

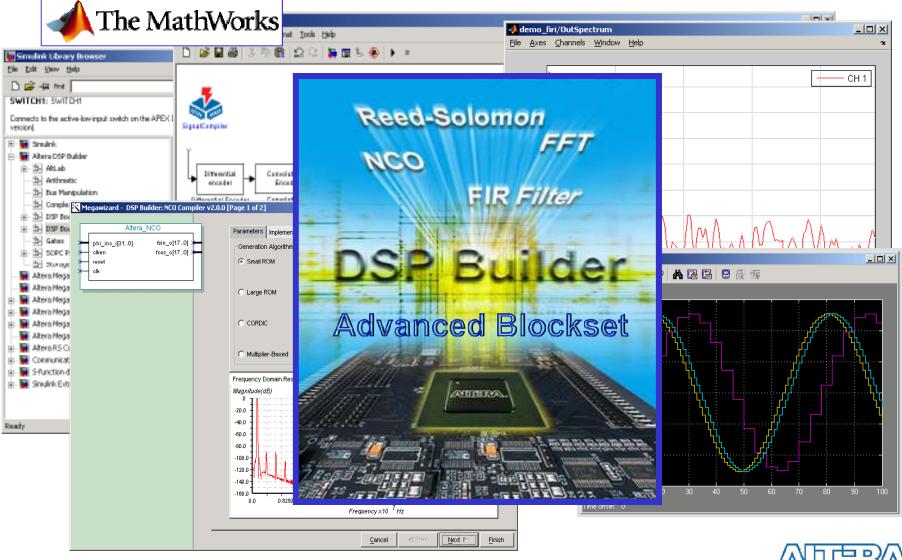

### Altera DSP Builder – Quick Algorithm Implementation

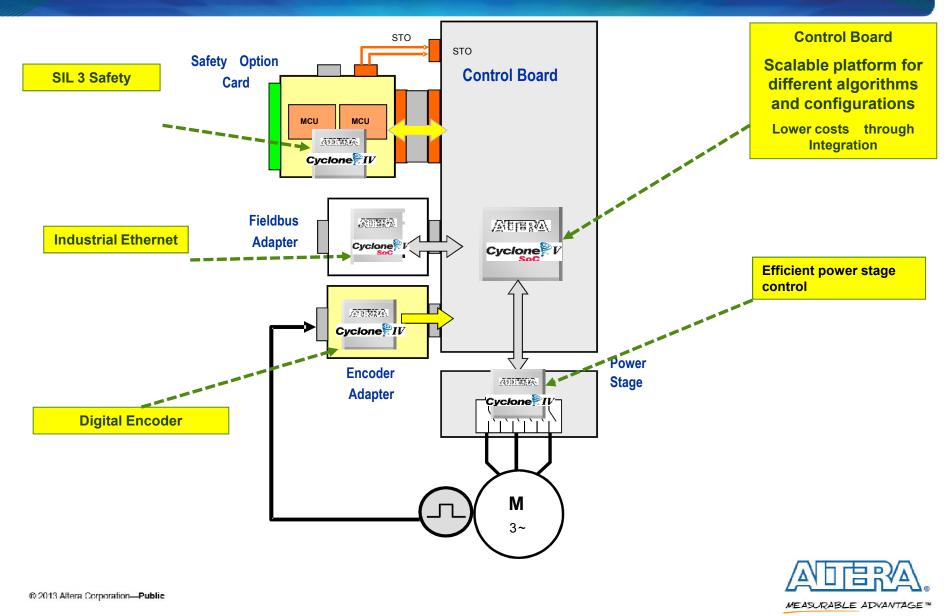

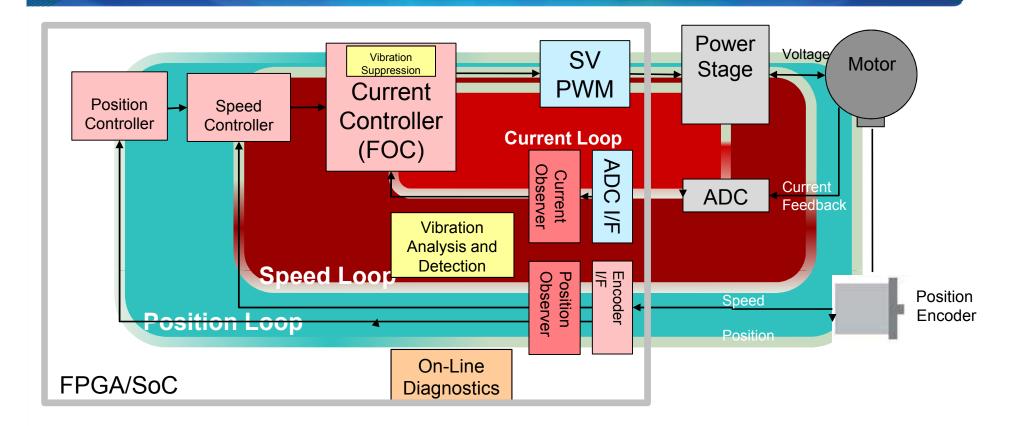

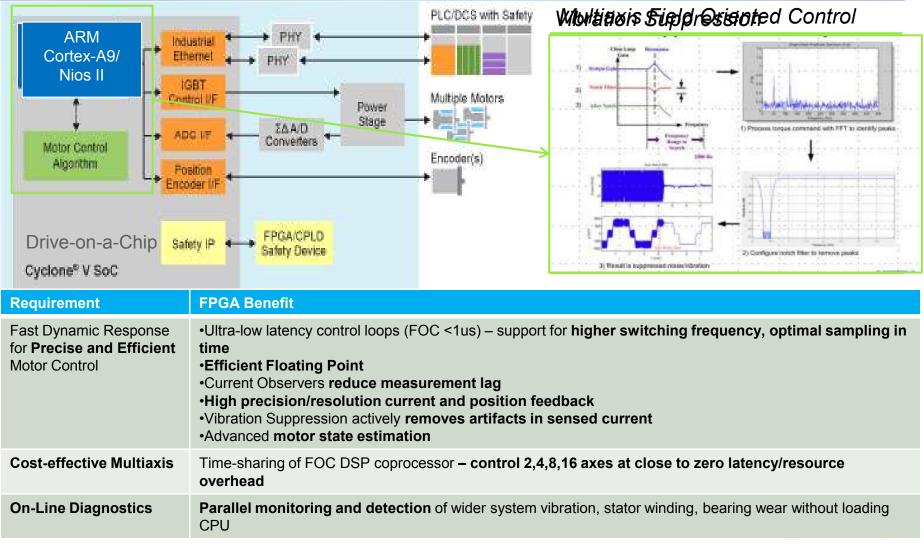

## **Drive-on-a-Chip Reference Design Overview**

- Integrated Multi-Axis Drive-on-a-Chip on Cyclone FPGA

- Software-only and FPGA Accelerated Implementations of multi-axis motor control

- Motor Control IP Suite

- FOC Control Loop IP

- Sigma-delta ADC I/F, PWM, Drive System Monitor

- Encoder IP (Partners)

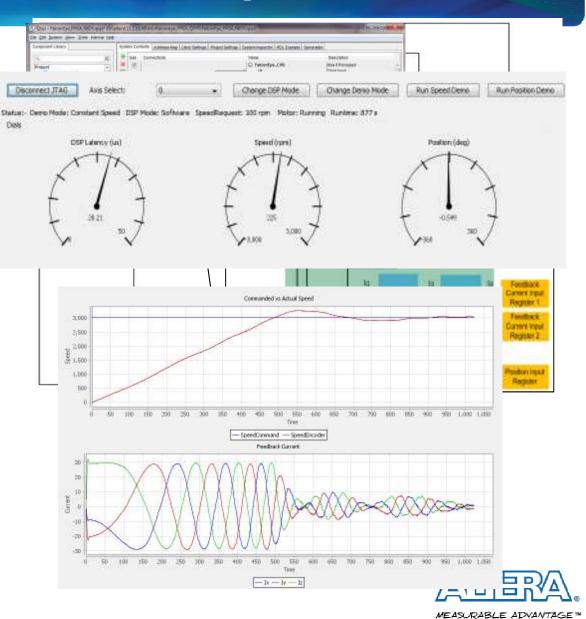

- Interactive Drive-on-a-Chip System Debug Tools

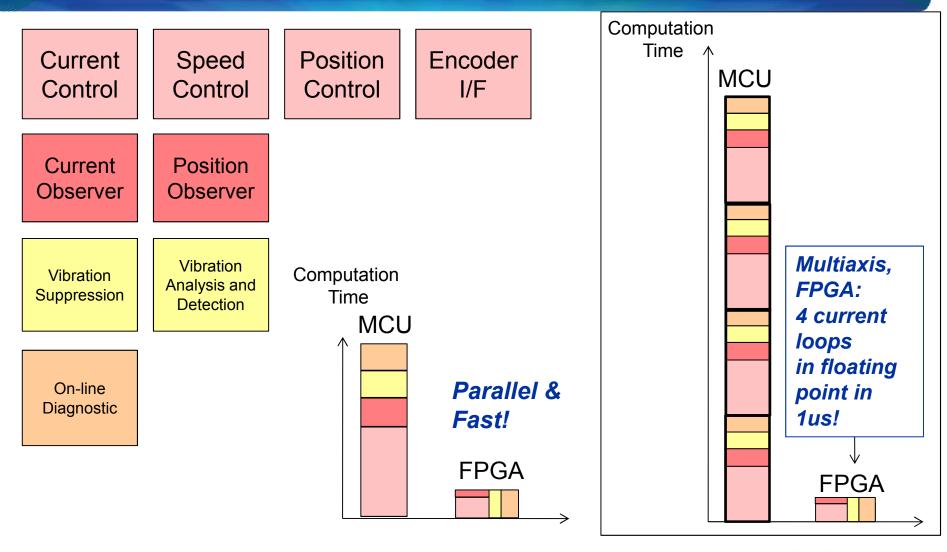

## Fast, Parallel Computation – Do Much More in Less Time

## Fast, Parallel Computation – Do Much More in Less Time

### Altera FPGA Drive-on-a-Chip – Scalable Performance

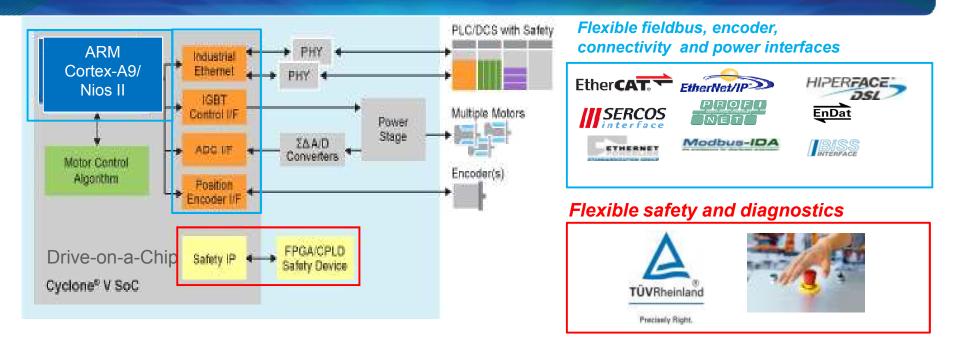

### **Altera FPGA Drive-on-a-Chip – Flexibility**

| Requirement                                 | FPGA Benefit                                                                                                                  |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Multiple Ethernet Protocols                 | All major protocols, custom switch implementations in FPGA fabric                                                             |

| Varying and evolving power stage interfaces | "Limitless" PWM interface count, 2L/3L inverters, flexibility in ADC support requirements                                     |

| Varying Encoder Protocols                   | High Performance Endat, BiSS, Hiperface Master support, configurable number of interfaces/axes, Custom/Proprietary interfaces |

| Functional Safety                           | Reduced Cost, T2M & Risk - Functional Safety Data Package, Safe/Non-Safe Partitioning                                         |

|                                             |                                                                                                                               |

## **Available Hardware Platforms**

Falconeye Motor Control

| Reference Design                                                                                               | Board Support                                              | Comments                                                                                  |

|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Altera Multi-axis FOC in fixed and floating point                                                              | INK CIV, Altera CV + Multiaxis<br>Motor Control Board      | MMC Board available for sale end Q1. Est Price: 2000 USD                                  |

| Altera Single-axis FOC in fixed and floating point                                                             | Falconeye Motor Control Kit<br>supporting CIV, CV (Feb'13) | Single-axis variation of<br>multiaxis design. (Price 2500,<br>includes CIV/CV FGPA Board) |

| EBV/U Cologne Drive Reference Design<br>Single-axis, Nios II floating-point design<br>with custom instructions | Falconeye Motor Control Kit<br>(CIV, CV)                   | Reference design ships with<br>Falconeye Kit (Price : 1800 EU<br>before shipping)         |

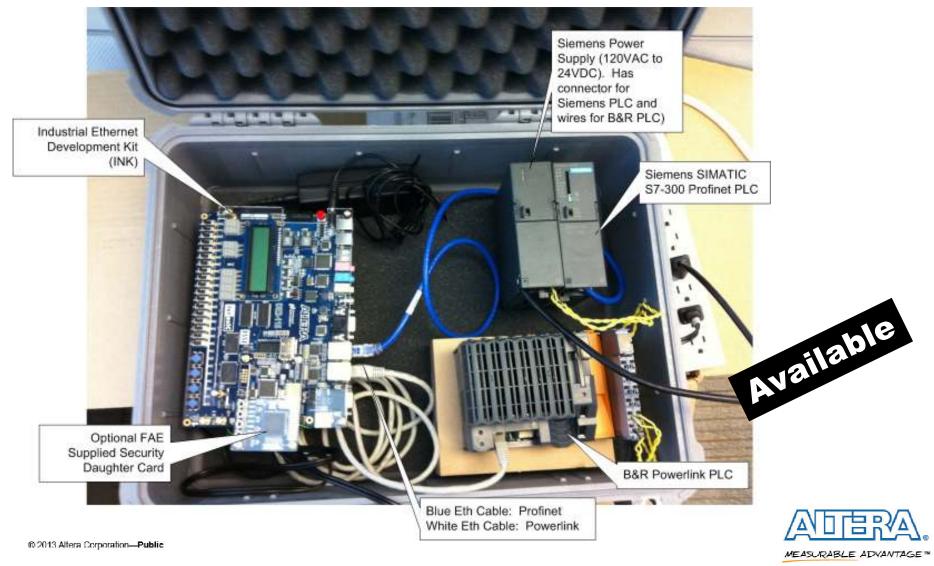

### **Field Demo Kits – Industrial Ethernet**

# **Thank You**

© 2013 Altera Corporation—Public

ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logus are inademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/legal.

MEASURABLE ADVANTAGE M