# **Global Clock Networks**

The Actel architecture provides global clock networks that allow high fanout drive for flip-flops and latches with minimal skew. Table 1 shows the available global networks and their characteristics, which are defined as follows.

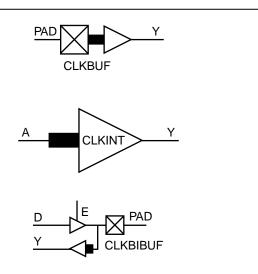

- Routed clocks are clock networks which can be used by selecting CLKBUF/CLKBIBUF or CLKINT macros or both.

- Dedicated clocks are clock networks that are directly wired to sequential and I/O modules. They contain no programming elements in the path from the I/O pad driver to the input of S-modules or I/O modules; they provide sub-nanosecond skew and guaranteed performance.

- A special network refers to a special hard-wired input for I/O modules that can only drive preset/clear pins of I/O modules.

Note that the *Internal Drive Option* for ACT<sup>™</sup> 2, 1200XL, 3200DX, and ACT 3 devices can only be utilized by selecting the CLKINT macro to drive an internal clock network.

### **ACT 1 Clock Network**

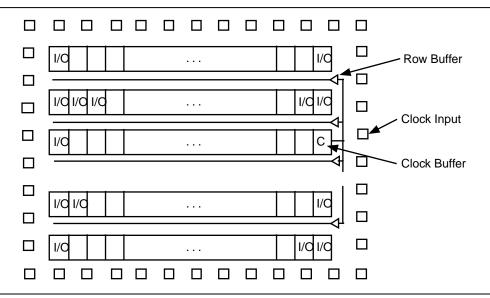

A single clock distribution network is provided on ACT 1 arrays. The clock network provides unlimited fanout (the ability to drive all logic modules in the array) with minimal delay and skew time. Figure 1 illustrates the clock

distribution network for an A1010 array. It is arranged similarly in the A1020 array.

The network is driven by a specific I/O pin that drives a dedicated on-chip buffer tree. Each row of logic modules (8 on the A1010 and 14 on the A1020) has a dedicated buffered clock track. The clock distribution network is selected automatically when the CLKBUF macro is used in the schematic and assigned to its dedicated package pin. The CLK I/O pin can also be used for normal I/Os by assigning INBUF, OUTBUF, TRIBUFF, or BIBUF to the CLK pin location.

### Clock Balancing Scheme

Clock balancing equalizes the clock loads on each branch of the global clock network, thereby minimizing clock skew. Clock skew can cause setup and hold time problems. The clock balancing strength sets the level of clock balancing for ACT 1 designs only. It is not used for ACT 2 and ACT 3 designs because the global clock networks for those families have been designed for minimal clock skew. The results are design dependent. If more than 50 percent of the logic modules are driven by the global clock, the effect is minimal. Also, strong clock balancing may result in increased delays and reduced routability.

**Table 1** • Global Clock Attributes

| Input Pad<br>Name | Туре      | Family                      | Number | Internal<br>Drive<br>Option | Macro                          | Note                                       |

|-------------------|-----------|-----------------------------|--------|-----------------------------|--------------------------------|--------------------------------------------|

| CLK               | routed    | ACT 1                       | 1      | No                          | CLKBIBUF,<br>CLKBUF            | Can adjust skew with clock balancing       |

| CLKA,<br>CLKB     | routed    | ACT 2,<br>1200XL,<br>3200DX | 2      | Yes                         | CLKBIBUF,<br>CLKBUF,<br>CLKINT | Use CLKINT for Internal Drive Option       |

| CLKA,<br>CLKB     | routed    | ACT 3                       | 2      | Yes                         | CLKBIBUF,<br>CLKBUF,<br>CLKINT | Use CLKINT for Internal Drive Option       |

| HCLK              | dedicated | ACT 3                       | 1      | No                          | HCLKBUF                        | Connected to all S-modules                 |

| IOCLK             | dedicated | ACT 3                       | 1      | No                          | IOCLKBUF                       | Connected to all I/O modules               |

| IOPCL             | special   | ACT 3                       | 1      | No                          | IOPCLBUF                       | Connected to I/O module set and reset pins |

| QCLK              | dedicated | 3200DX                      | 4      | Yes                         | QCLKINT<br>QCLKBUF             | Use QCLKINT for Internal Drive Option      |

Figure 1 • Clock Distribution Network for an A1010

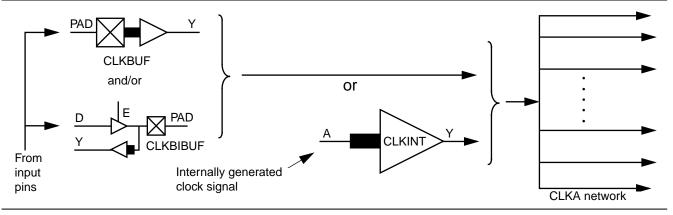

Figure 2 • One of Two ACT 2/1200XL/3200DX Family Clock Networks (CLKO)

## ACT 2, 1200XL, and 3200DX Clock Networks

Two low-skew, high fanout clock distribution networks are provided in the ACT 2, 1200XL, and 3200DX architectures. Figure 2 illustrates the implementation of one of two clock networks using CLKBUF/CLKBIBUF or CLKINT macro or both. ACT 2, 1200XL, and 3200DX devices offer two identical clock networks. The clock modules are located in the top row of I/O modules. Clock drivers and a dedicated horizontal clock track are located in each horizontal routing channel. The clock input pads may also be used as normal I/Os, bypassing the clock networks. These networks are referred to as CLKA and CLKB. Each network has a clock module that selects the source of the clock signal and may be driven as follows:

- externally from the CLKBUF macro

- externally from the CLKBIBUF macro

- internally from the CLKINT macro

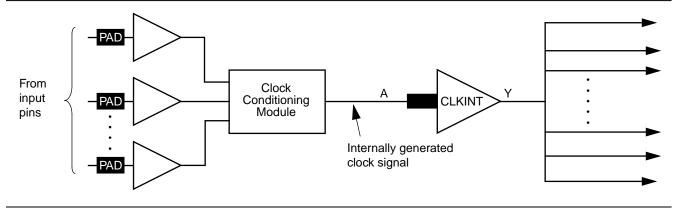

As mentioned above, the macro CLKBUF is used to connect one of the two external clock pins to a clock network, and the macro CLKINT is used to connect an internally generated clock signal to a clock network. Figure 3 illustrates the implementation of internal clock network using CLKINT macro. In the figure, the input signals are driven by regular I/O buffers, not CLKBUF or CLKBIBUF. These input signals drive a user-created Clock Conditioning Module, which generates the internal clock signal. This signal is subsequently driven by the CLKINT macro.

The 3200DX family has an additional clock network, the "quadrant" clock.

#### Quadrant Clocks

The 3200DX offers four additional "quadrant" clocks. These clock networks are accessed by special I/Os, QCLKBUF, or internally using the macro, QCLKINT.

Figure 3 • Implementation of Internal Clock Network Using CLKINT Macro

The quadrant clocks are high-speed, low-skew routes dedicated to providing suitable paths for high-speed clocks.

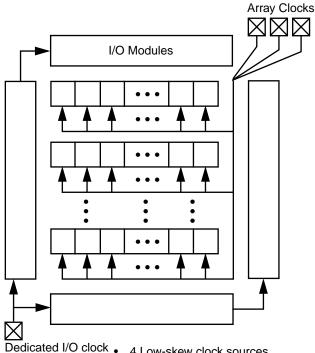

#### **ACT 3 Clock Networks**

- 4 Low-skew clock sources

- Dedicated I/O clock

- Dedicated array clock

- Two routed array clocks (like ACT 2 family)

- Can tie dedicated clocks together for fully synchronous operation

Figure 4 • ACT 3 Family Clock Networks

The ACT 3 architecture contains four clock networks: two high performance dedicated clock networks and two general

purpose routed networks. The high performance networks function at up to 250 MHz, while the general purpose routed networks function at up to 150 MHz. Figure 4 illustrates the ACT 3 family clock networks.

#### **Dedicated Clocks**

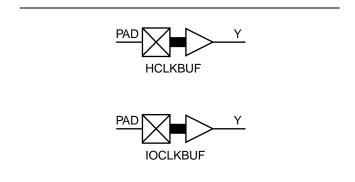

There are two dedicated clock networks: one for the array registers known as Dedicated Array Clock (HCLK) and one for the I/O registers known as Dedicated I/O Clock (IOCLK) The clock networks are accessed by special I/Os. Figure 5 shows the macros that drive the Dedicated Array and I/O clock networks in ACT 3 devices.

Figure 5 • Dedicated Array and I/O Clock Buffers

HCLK is a dedicated hard-wired clock input for sequential modules. HCLK is directly wired to each S-module and offers guaranteed clock speeds independent of the number of S-modules being driven. IOCLK is a dedicated hard-wired clock input for I/O modules. IOCLK is directly wired to each I/O module and offers guaranteed clock speeds independent of the number of I/O modules being driven. These dedicated clock networks support high performance by providing sub-nanosecond skew and guaranteed performance. Dedicated clock networks contain no programming elements in the path from the I/O pad driver to the input of S-modules or I/O modules.

#### Routed Clocks

The routed clock networks for ACT 3 devices have the same characteristics as the ACT 2, 1200XL, and 3200DX networks as shown in Figure 2 and Figure 3. The macros that drive routed clock networks in ACT 1, ACT 2, 1200XL, 3200DX, and ACT 3 devices are shown in Figure 6.

Figure 6 • Dedicated Routed Clock Buffers

CLKA and CLKB are global signals with unlimited fanout. Refer to ACT 2 family clock networks described above for more detail on ACT 3 family routed clocks.

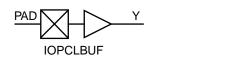

Special Hard-wired Preset/Clear Network

IOPCL is a dedicated special hard-wired input for I/O modules. It is directly wired to the Preset and Clear inputs of all I/O registers. IOPCL functions as an I/O when no I/O preset or clear macros are used. Figure 7 shows the IOPCLBUF macro that drives the dedicated hard-wired Preset/Clear network. IOPCLBUF can only be connected to the preset/clear pins of I/O macros.

Figure 7 • Dedicated Preset/Clear Network Buffer

The routed clocks CLKA and CLKB can also be used to drive high fanout nets like resets, output enables, or data enables. This saves logic modules and results in performance increases in some cases.

# Clock Connections for ACT 2, 1200XL, 3200DX, and ACT 3 Families

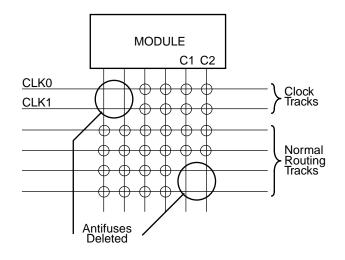

To minimize loading on the clock networks, only a subset of module inputs has antifuses on the clock tracks. Therefore, only a few of the C-module and S-module inputs can be connected to the clock networks. To further reduce loading on the clock network, only a subset of the horizontal routing tracks can connect to the clock inputs of the S-module. Figure 8 illustrates the connections to the clock networks.

## Creating a User-Defined Clock Distribution Network

Some applications require many internal clock networks. For these type of designs or for clock networks with a small number of loads, it may be better to create a user-defined clock network. Because this clock network is not a built-in, dedicated circuit, the skews and delays cannot be guaranteed.

However, by intelligently placing the I/O pins and declaring the nets associated with the clock network as critical, the automatic placement of these macros create a network that controls clock skew and delay. The results can be verified by running a simulation or using the Actel Designer Series software. It may be necessary to place and route again to meet timing requirements. To minimize the skew between paths, try to equalize the loading in each leg of the clock distribution network.

Figure 8 • Fuse Deletion on Clock Networks